视觉信息处理与FPGA实现第三次作业-7人表决器

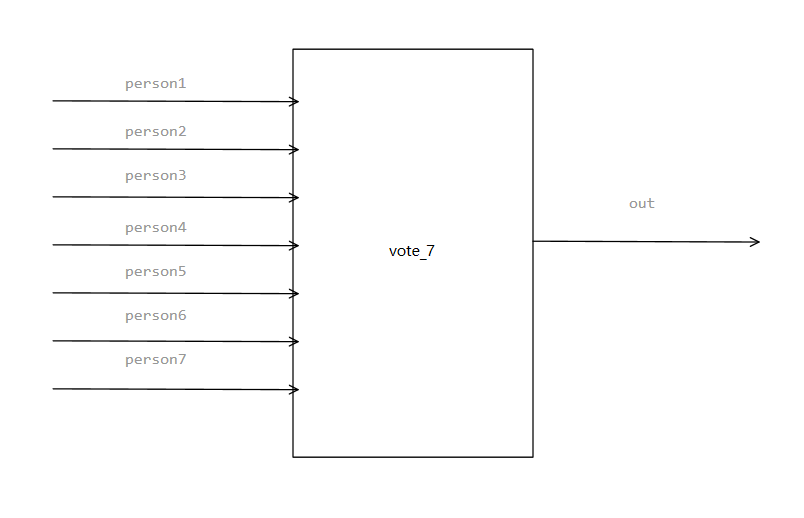

一、模块端口图

二、代码

`timescale 1ns / 1ns

module vote_7(person1,person2,person3,person4,person5,person6,person7,out);

input person1,person2,person3,person4,person5,person6,person7 ;

output out ;

assign out=(person1+person2+person3+person4+person5+person6+person7>= 4) ? 1 : 0;

endmodule

三、testbench

`timescale 1ns / 1ps

module vote_7_tb();

reg person1,person2,person3,person4,person5,person6,person7;

wire result;

vote_7 vote_7(

.person1 ( person1 ),

.person2 ( person2 ),

.person3 ( person3 ),

.person4 ( person4 ),

.person5 ( person5 ),

.person6 ( person6 ),

.person7 ( person7 ),

.out ( result )

);

initial begin

//The truth table for a 7-bit binary has a total of 128 entries.

//So here we list 7 situation

person1=0 ;person2=0 ;person3=0 ;person4= 0; person5= 0; person6= 0; person7= 0;

#100

person1=1 ;person2=0 ;person3=0 ;person4= 0; person5= 0; person6= 0; person7= 0;

#100

person1=1 ;person2=1 ;person3=0 ;person4= 0; person5= 0; person6= 0; person7= 0;

#100

person1=1 ;person2=1 ;person3=1 ;person4= 0; person5= 0; person6= 0; person7= 0;

#100

person1=1 ;person2=1 ;person3=1 ;person4= 1; person5= 0; person6= 0; person7= 0;

#100

person1=1 ;person2=1 ;person3=1 ;person4= 1; person5= 1; person6= 0; person7= 0;

#100

person1=1 ;person2=1 ;person3=1 ;person4= 1; person5= 1; person6= 1; person7= 0;

#100

person1=1 ;person2=1 ;person3=1 ;person4= 1; person5= 1; person6= 1; person7= 1;

#100

$stop;

end

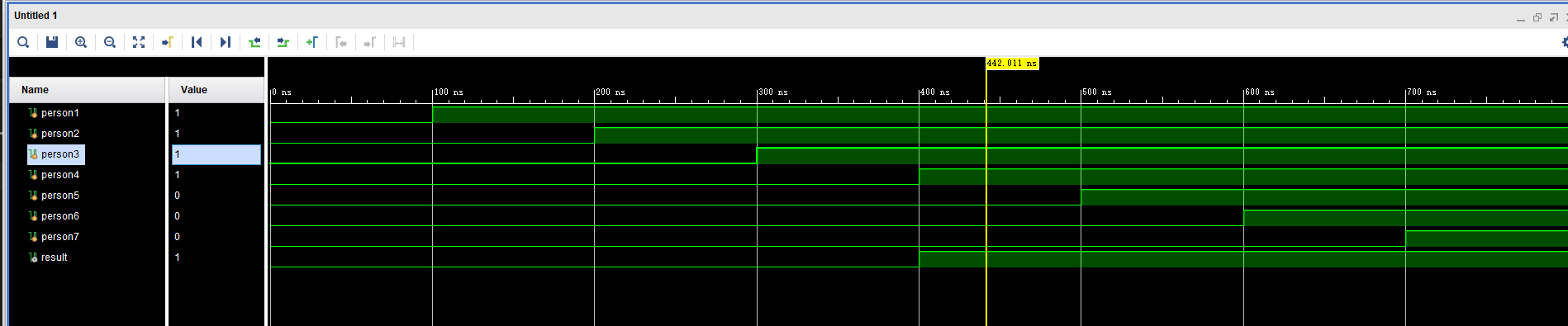

endmodule四、Vivado仿真图像

可以看到随着投票人数的增多,result最终在同意人数到达4的时候,输出1,即通过。

五、代码风格

注意对齐和易读性,另外注释尽量用英文,顺便学习相关专业名词。