【Ethernet】以太网卡LAN8720A分析和使用

文章目录

1. LAN8720A简介

2. PHYAD[0]: PHY地址配置

3. MODE[2:0]: Mode配置

4. nINTSEL: nINT/REFCLKO配置

5. REGOFF: 配置内部+1.2V电压源

6.SMI(MDC/MDIO)总线接口介绍

6.1 MDIO接口

6.2 MDIO数据传输协议

7. 相关寄存器描述

8. 参考资料

1. LAN8720A简介

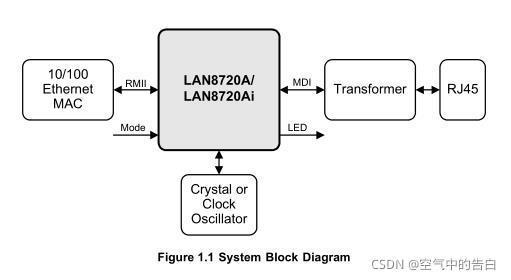

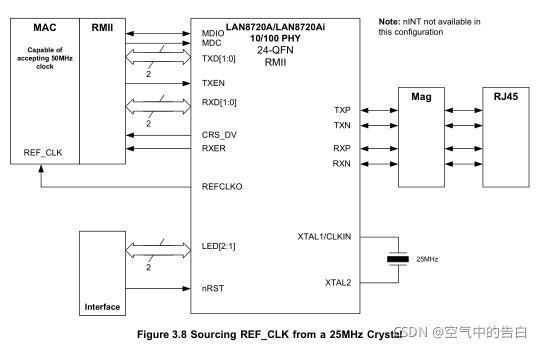

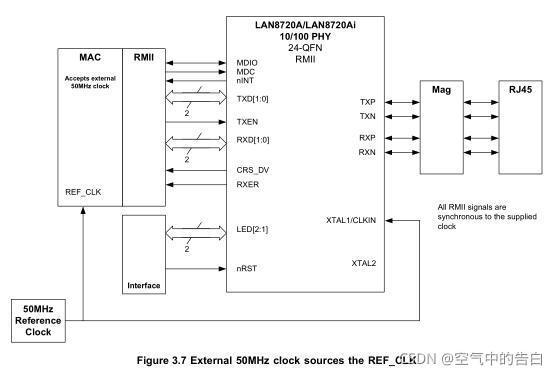

LAN8720A 是 SMSC 公司(已被 Microchip公司收购)设计的一个体积小、功耗低、全能型 10/100Mbps 的以太网物理层收发器。它是针对消费类电子和企业应用而设计的。LAN8720A总共只有 24Pin,仅支持 RMII接口。由它组成的网络结构如下图所示:

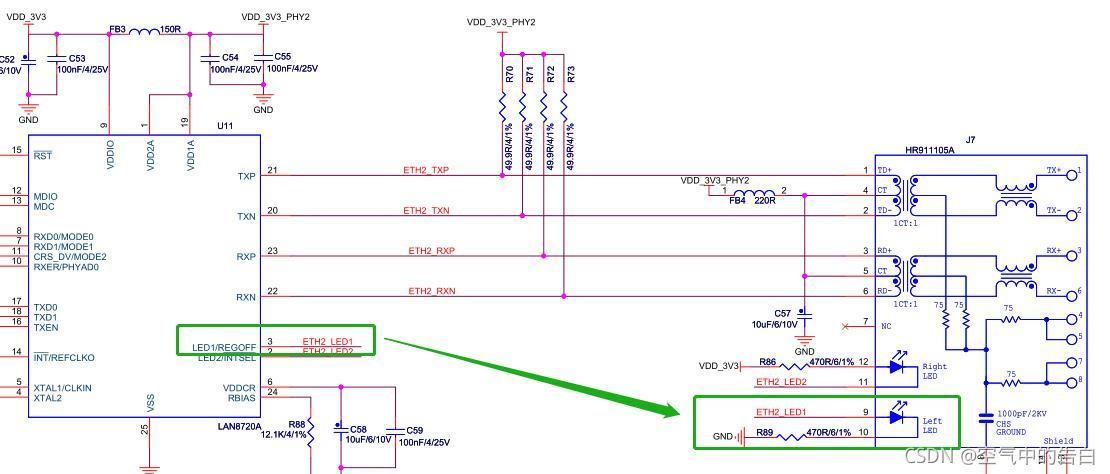

LAN8720A 通过 RMII与 MAC连接。RJ45是网络插座,在与 LAN8720A 连接之间还需要一个变压器,所以一般使用带电压转换和 LED 指示灯的 HY911105A型号的插座。一般来说,必须为使用 RMII接口的 PHY提供 50MHz的时钟源输入到 REF_CLK引脚,不过LAN8720A内部集成 PLL,可以将 25MHz的时钟源陪频到 50MHz 并在指定引脚输出该时钟,所以我们可以直接使其与 REF_CLK连接达到提供 50MHz时钟的效果。

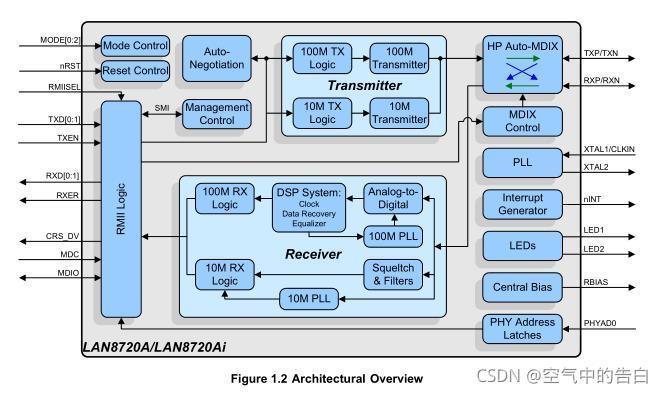

LAN8720A 内部系统结构如下图所示:

LAN8720A 有各个不同功能模块组成,最重要的是数据接收控制器和发送控制器,其它的基本上都是与外部引脚挂钩,实现信号传输。部分引脚是具有双重功能的,比如PHYAD0与 RXER 引脚是共用的,在系统上电后 LAN8720A 会马上读取这部分共用引脚的电平,以确定系统的状态并保存在相关寄存器内,之后则自动转入作为另一功能引脚。

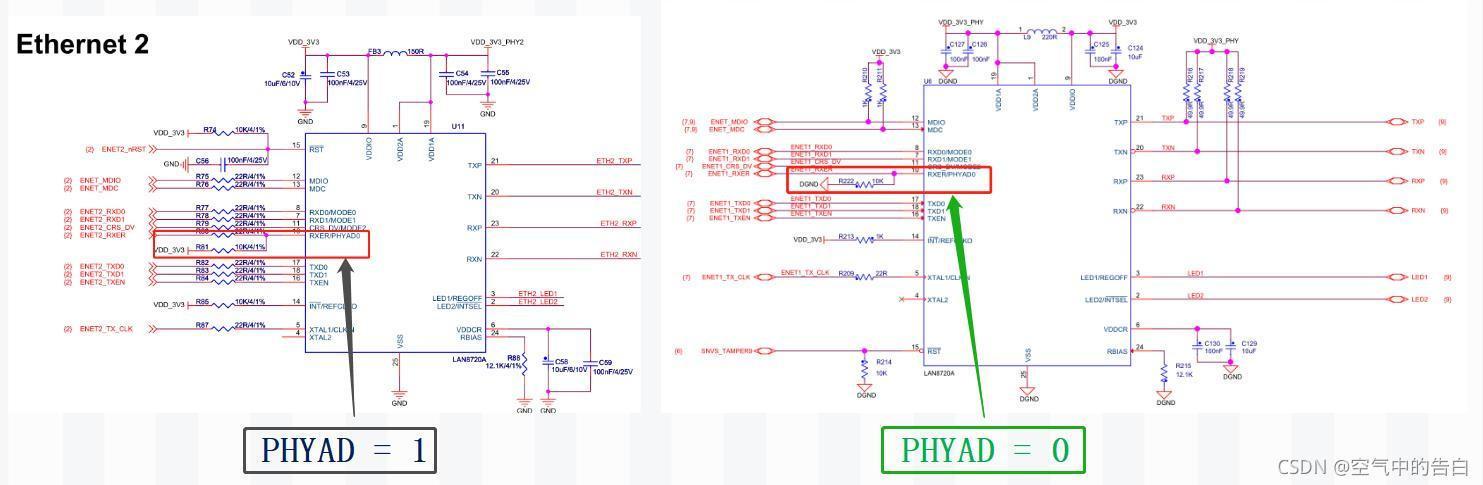

2. PHYAD[0]: PHY地址配置

PHYAD[0]引脚用于配置 SMI通信的 LAN8720A 地址,在芯片内部该引脚已经自带下拉电阻,默认认为 0(即使外部悬空不接),在系统上电时会检测该引脚获取得到 LAN8720A的地址为 0 或者 1,并保存在特殊模式寄存器(R18)的 PHYAD位中,该寄存器的 PHYAD有 5个位,在需要超过 2个 LAN8720A 时可以通过软件设置不同 SMI通信地址。

下面是LAN8720A实际中,硬件默认对PHY地址的配置如下:

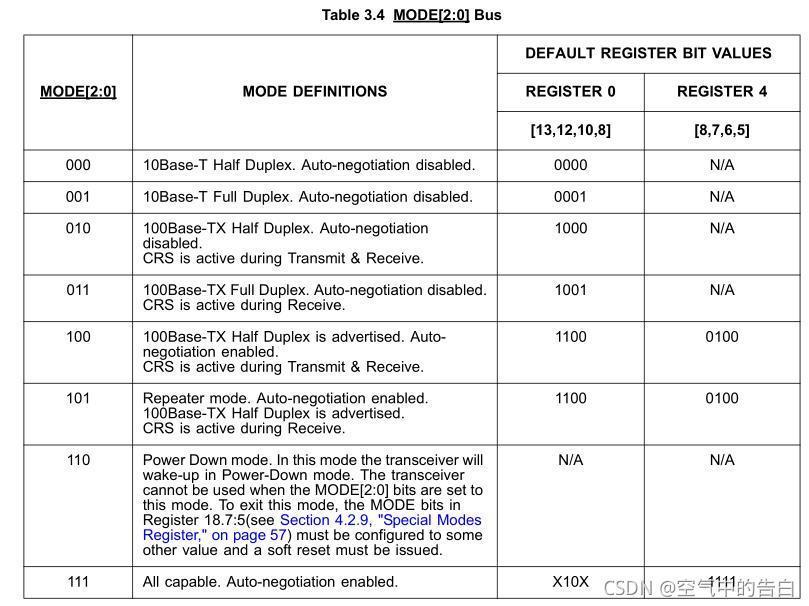

3. MODE[2:0]: Mode配置

MODE[2:0]引脚用于选择 LAN8720A 网络通信速率和工作模式,可选 10Mbps 或 100Mbps 通信速度,半双工或全双工工作模式。另外 LAN8720A 支持 HP Auto-MDIX 自动翻转功能,即可自动识别直连或交叉网线并自适应。一般将 MODE 引脚都设置为 1,可以让 LAN8720A 启动自适应功能,它会自动寻找最优工作方式。MODE[0]与 RXD0 引脚共用、MODE[1]与 RXD1 引脚共用、MODE[2]与 CRS_DV 引脚共用,具体如下:

| MODE BIT | PIN NAME |

| MODE[0] | RXD0/MODE0 |

| MODE[1] | RXD1/MODE1 |

| MODE[2] | CRS_DV/MODE2 |

通过以上的 MODE[2:0] 硬件配置引脚,可以支持以下几种模式:

4. nINTSEL: nINT/REFCLKO配置

4. nINTSEL: nINT/REFCLKO配置

通过nINTSEL来配置两个模式:REF_CLK输入模式(nINT)和REF_CLK输出模式。通过该引脚的高低电平决定了nINT / REFCLKO引脚的功能。

| STRAP | VALUE | MODE | REF_CLK DESCRIPTION |

| nINTSEL | 0 | REF_CLK Out Mode | nINT/REFCLKO is the source of REF_CLK |

| nINTSEL | 1 | REF_CLK In Mode | nINT/REFCLKO is the source of REF_CLK |

当 nINTSEL引脚为低电平时,它也可以被设置成 50MHz 时钟输出,这样可以直接与 主机MAC接口 的 REF_CLK引脚连接为其提供 50MHz时钟源,这种模式要求为 XTAL1 与 XTAL2 之间或为 XTAL1/CLKIN提供 25MHz时钟,由 LAN8720A内部 PLL电路陪频得到 50MHz 时钟,此时nIN/REFCLKO 引脚的中断功能不可用,用于 50MHz时钟输出。

当 nINTSEL引脚为高电平时,LAN8720A 被设置为时钟输入,即外部时钟源直接提供 50MHz时钟接入 主机MAC接口的 REF_CLK引脚和 LAN8720A 的 XTAL1/CLKIN 引脚,此时 nINT/REFCLKO 可用于中断功能。nINTSEL与 LED2引脚共用。

5. REGOFF: 配置内部+1.2V电压源

REGOFF引脚用于配置内部+1.2V电压源,LAN8720A 内部需要+1.2V电压,可以通过VDDCR引脚输入+1.2V 电压提供,也可以直接利用 LAN8720A 内部+1.2V 稳压器提供。当REGOFF引脚为低电平时选择内部+1.2V稳压器。REGOFF与 LED1 引脚共用。

由于REGOFF的配置与LED1引脚共享功能,因此还必须适当考虑LED的极性。下面是REGOFF引脚为低电平时的实例如下:

6.SMI(MDC/MDIO)总线接口介绍

6.1 MDIO接口

SMI:串行管理接口(Serial Management Interface),也被称作MII管理接口(MII Management Interface),包括MDC和MDIO两条信号线。MDIO是一个PHY的管理接口,用来读/写PHY的寄存器,以控制PHY的行为或获取PHY的状态,MDC为MDIO提供时钟。

MDIO原本是为MII总线接口定义的,MII用于连接MAC和PHY,包含两种信号接口:

1: 一个数据接口用于MAC和PHY之间接收和发送以太网帧数据。

2: 一个PHY管理接口,即MDIO,用于读写每个PHY的控制寄存器和状态寄存器,以达到控制PHY行为和监控PHY状态的目的。

MDIO是双向的,只支持一个MAC连接最多32个PHY的连接方式,且MAC作为master,PHY作为slave。在写PHY寄存器的时候,由MAC驱动MDIO向PHY写入数据;在读PHY寄存器时,前半段由MAC驱动发送寄存器地址,后半段由PHY驱动回复寄存器的值。

MDC要求由MAC输出,是非周期性的,即不要求提供固定频率的时钟,对于PHY芯片则作为输入,以在上升沿触发MDIO的读写。MDC的时钟频率可以是DC-2.5MHz,即最小的时钟周期为400ns。

6.2 MDIO数据传输协议

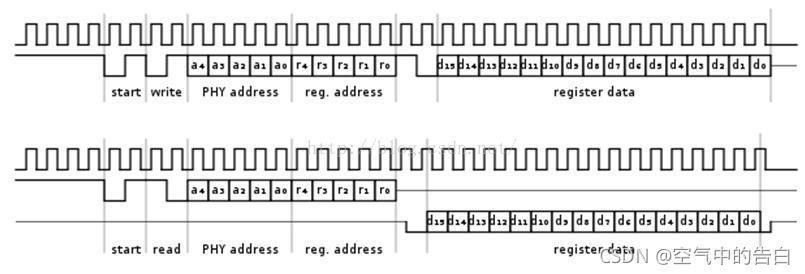

MDIO数据格式定义在IEEE 802.3以太网标准中,如下图所示(数据传输顺序为从左至右)

Preamble Start OP Code PHYAD REGAD Turn Around Data Idle

(32bits)(2bits) (2bits) (5bits) (5bits) (2bits) (16bits)

Read 1…1 01 10 A4A3A2A1A0 R4R3R2R1R0 Z0 D15…D0 Z*

Write 1…1 01 01 A4A3A2A1A0 R4R3R2R1R0 10 D15…D0 Z*

上图中*表示高阻态,这时MDIO的状态由一个外部的1.5KΩ电阻决定。

Preamble+Start:32bits的前导码以及2bit的开始位。

OP Code:2bits的操作码,10表示读,01表示写。

PHYAD:5bits的PHY地址,一般PHY地址从0开始顺序编号,例如6口switch中PHY地址为0-5。

REGAD:5bits的寄存器地址,即要读或写的寄存器。

Turn Around:2bits的TA,在读命令中,MDIO在此时由MAC驱动改为PHY驱动,并等待一个时钟周期准备发送数据。在写命令中,不需要MDIO方向发生变化,则只是等待两个时钟周期准备写入数据。

Data:16bits数据,在读命令中,PHY芯片将读到的对应PHYAD的REGAD寄存器的数据写到Data中,在写命令中,MAC将要写入对应PHYAD的REGAD寄存器的值写入Data中。

Idle:空闲状态,此时MDIO无源驱动,处高阻状态,但一般用上拉电阻使其处在高电平。

需要注意的是,为了保证PHY能准确采样,当MAC向MDIO写数据的时候,需要在MDC的上升沿之前就把数据写到MDIO上,要求等待10ns以上再发出一个MDC的上升沿。而为了保证MAC能准确采样,当PHY向MDIO写数据时,这个clock-to-data的delay时间范围可以是0-300ns(小于上面提到的400ns)。这个规定使接口的实现变得简单,但一定程度上限制了总线带宽。

IEEE 802.3还定义了扩展的SMI数据格式,包括read,write以及set address和read increment,不过我们在此不做讨论。

7. 相关寄存器描述

SMI支持寻址 32 个寄存器,LAN8720A 只用到其中 14 个,具体如下:

| 序号 | 寄存器名称 | 分组 |

| 0 | Basic Control Register | Basic |

| 1 | Basic Status Register | Basic |

| 2 | PHY Identifier 1 | Extended |

| 3 | PHY Identifier 2 | Extended |

| 4 | Auto-Negotiation Advertisement Register | Extended |

| 5 | Auto-Negotiation Link Partner Ability Register | Extended |

| 6 | Auto-Negotiation Expansion Register | Extended |

| 17 | Mode Control/Status Register | Vendor-specific |

| 18 | Special Modes | Vendor-specific |

| 26 | Symbol Error Counter Register | Vendor-specific |

| 27 | Control / Status Indication Register | Vendor-specific |

| 29 | Interrupt Source Register | Vendor-specific |

| 30 | Interrupt Mask Register | Vendor-specific |

| 31 | PHY Special Control/Status Register | Vendor-specific |

序号与 SMI数据帧中的 RADDR是对应的,这在编写驱动时非常重要。寄存器可规划为三个组:Basic、Extended和 Vendor-specific。

Basic 是 IEEE802.3 要求的,R0 是基本控制寄存器,其位 15为 Soft Reset 位,向该位写 1启动LAN8720A 软件复位,还包括速度、自适应、低功耗等等功能设置。R1 是基本状态寄存器。

Extended 是扩展寄存器,包括 LAN8720A的 ID号、制造商、版本号等等信息。

Vendor-specific 是供应商自定义寄存器,R31 是特殊控制/状态寄存器,指示速度类型和自适应功能。

8. 参考资料

《零死角玩转STM32—F429挑战者.pdf》