数字逻辑电路(八)

数字逻辑电路(八)

目录

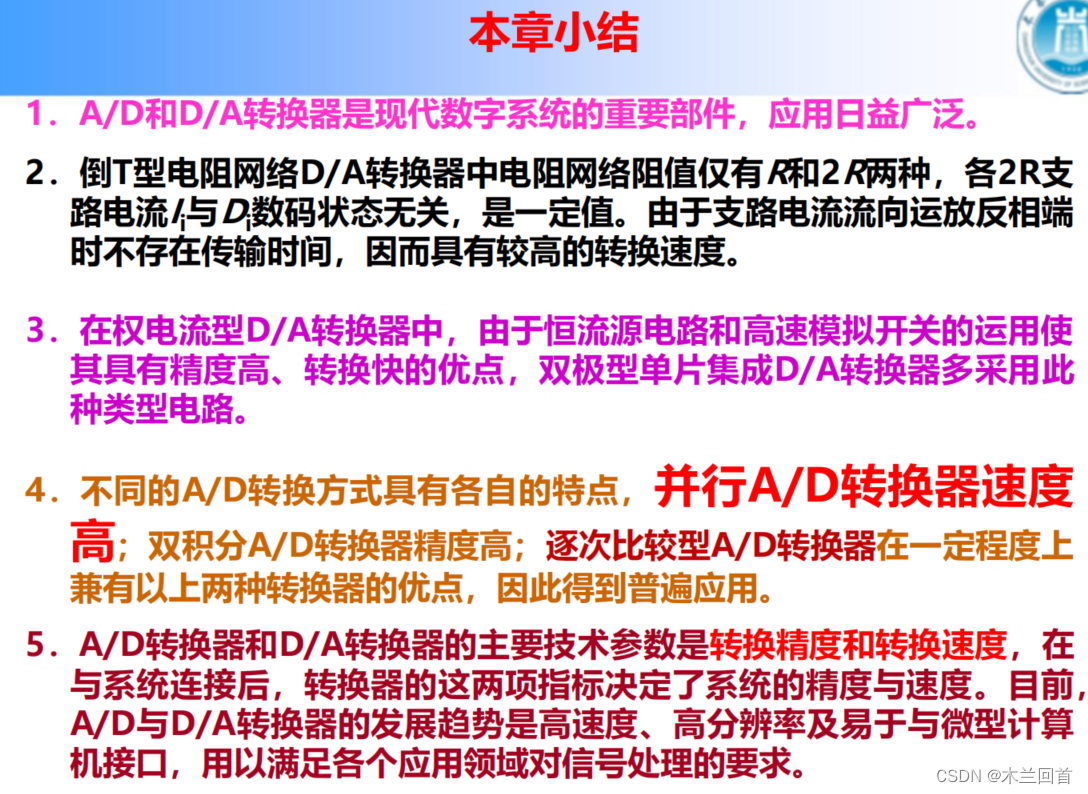

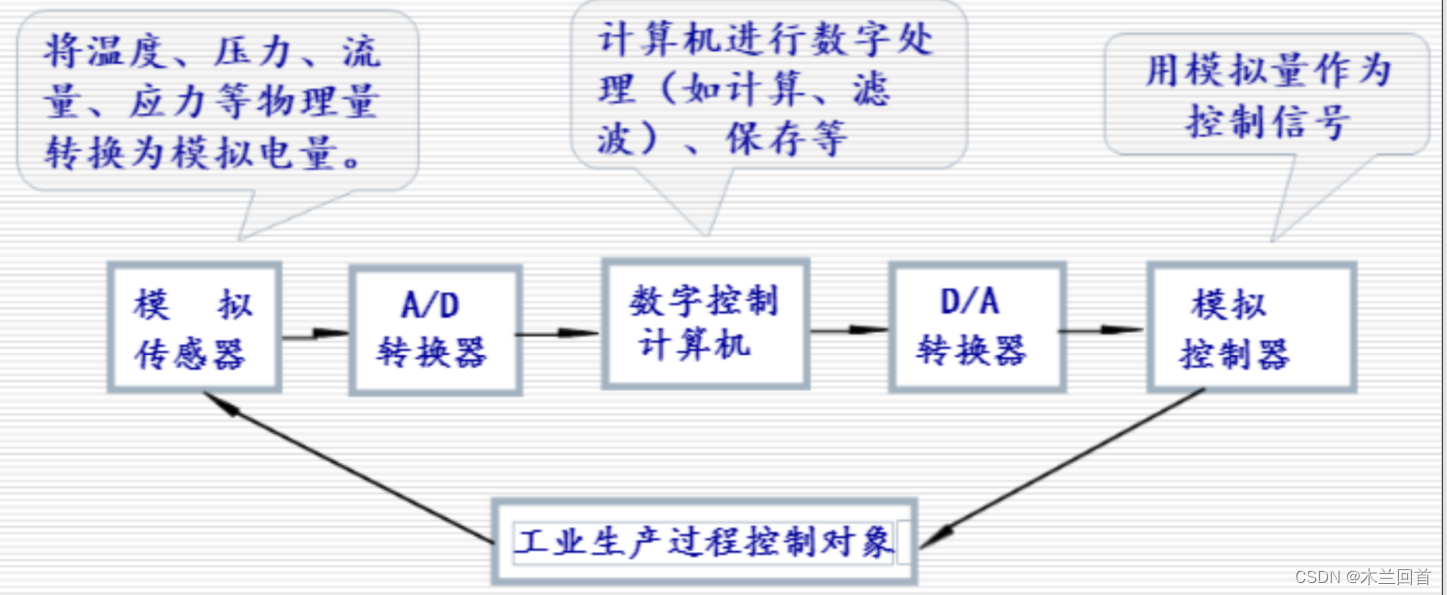

数模与模数转换电路

1.数字控制系统

ADC转换器:能将模拟信号转换成数字信号的电路,称为

模数

转换器

;

DAC转换器:将能把数字信号转换成模拟信号的电路,称为

数

模转换器。

2.数模转换器(DAC)

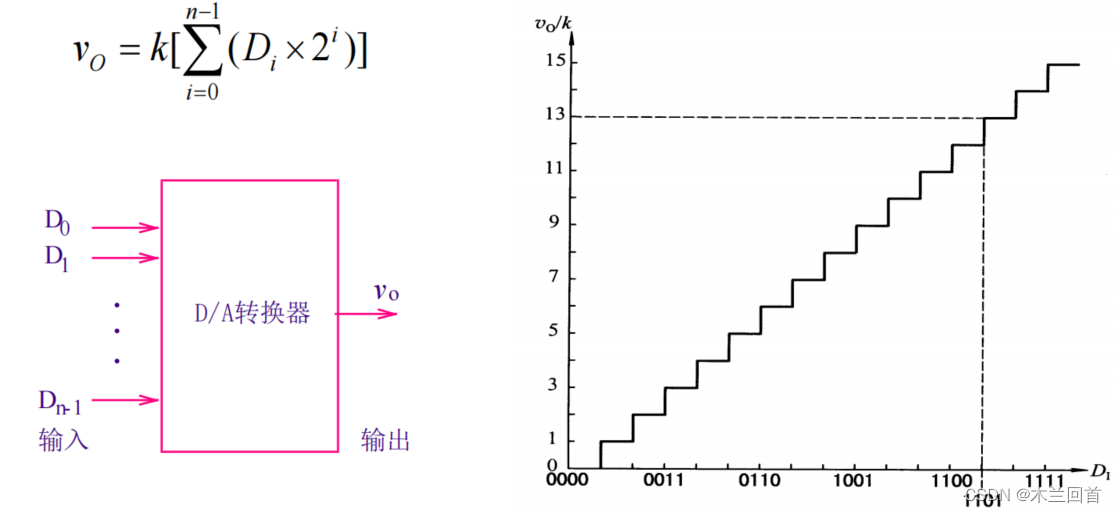

DAC的功能——将数字量成正比地转换与之对应成模拟量

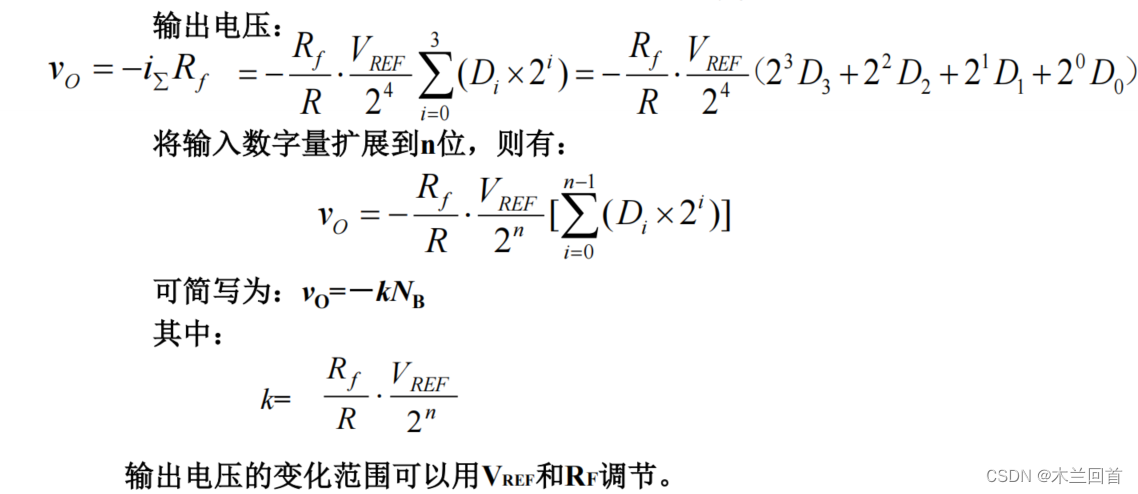

对于有权码,先将每位二进制代码按其权的大小转换成相应的模拟量,然后 将这些模拟量相加,即可得到与数字量成正比k(转换比例系数)的总模拟 量,从而实现了数字/模拟转换。

相邻两数码转换出的电压差值由

最低位码

所代表的电压的

位权值决定。

LSB

:信息所能分辨的最小值为1LSB

。

FSR:对应于最大数字量的最大电压输出值(绝对值)为

1FSR。

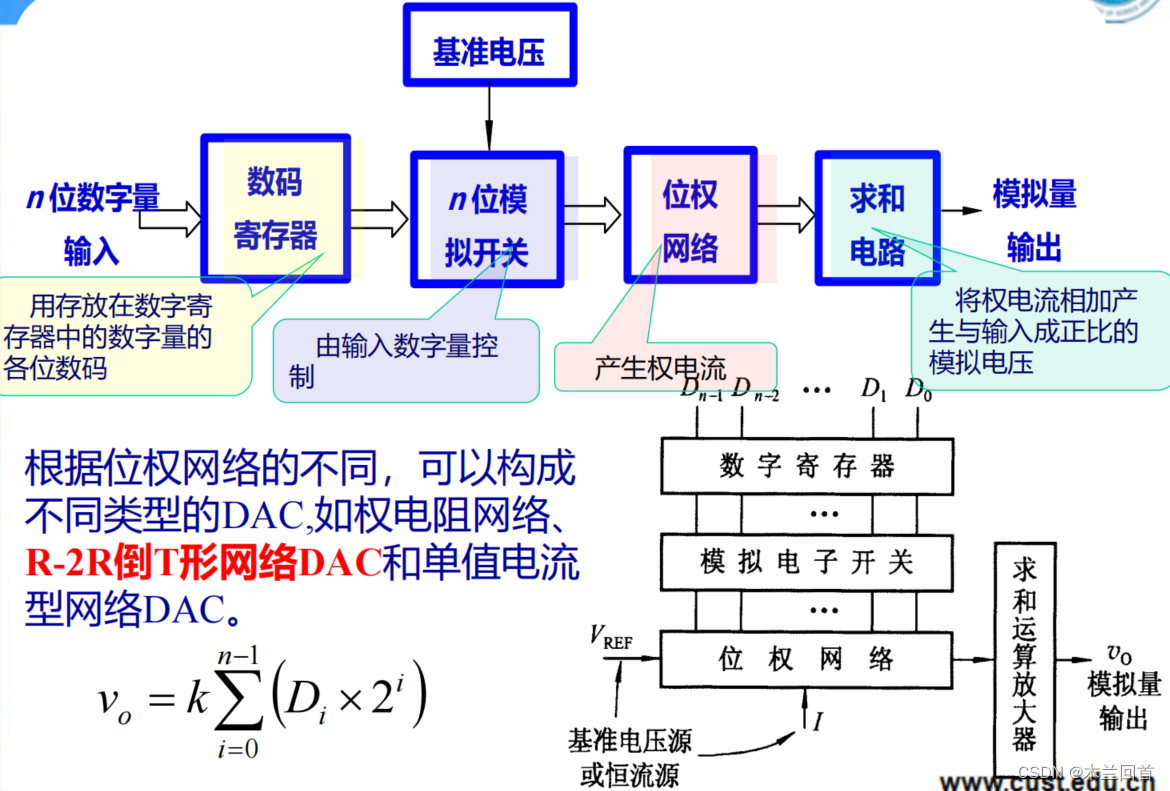

2.1DAC转换器的一般构成

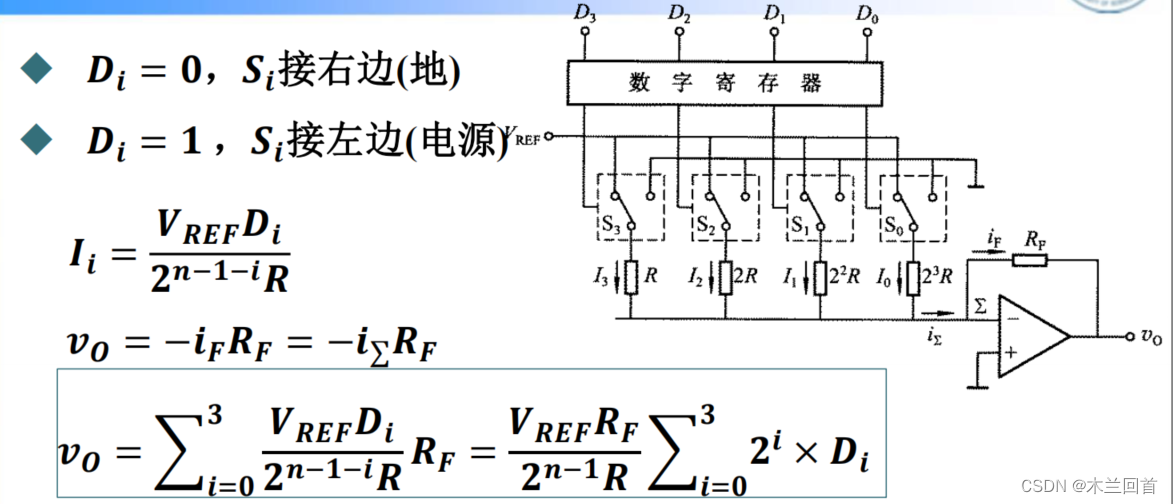

2.2权电阻网络

缺点

——各权电阻的阻值都

不相同

,

位数多

时,其阻值相差甚

远,这给保证精度带来很大困难,特别是对于集成电路的制作

很不利,因此在集成的 DAC 中

很少单独

使用该电路。

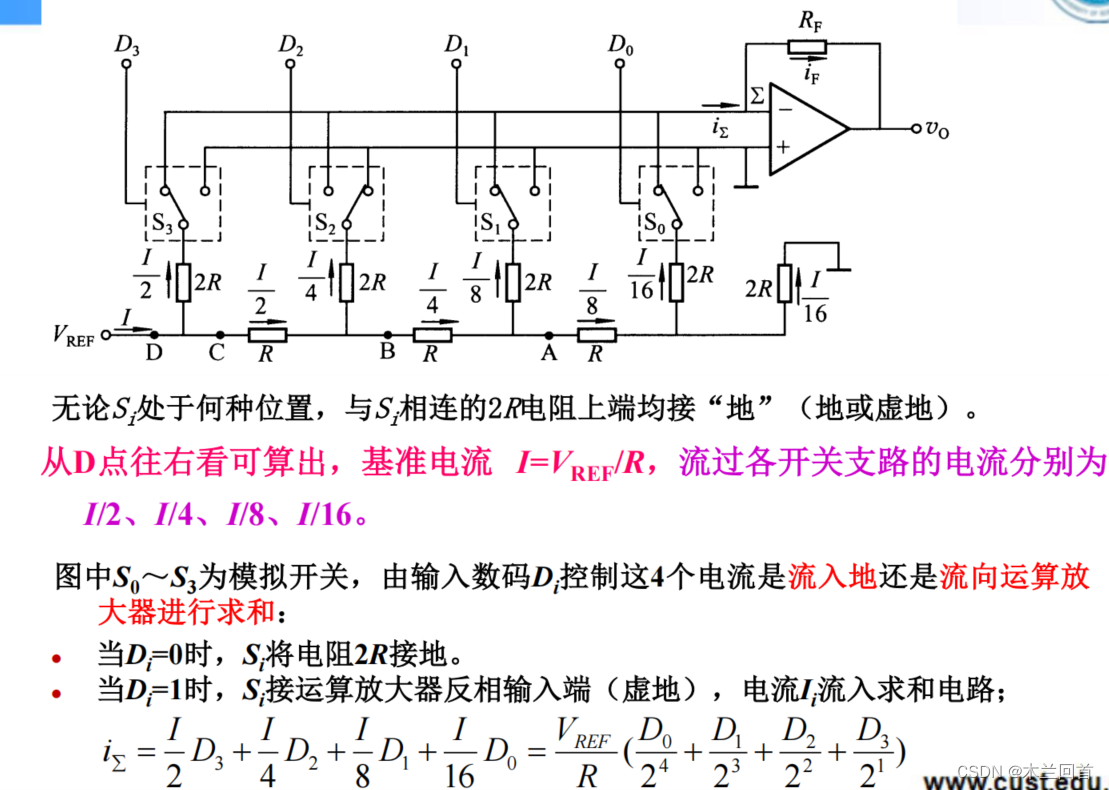

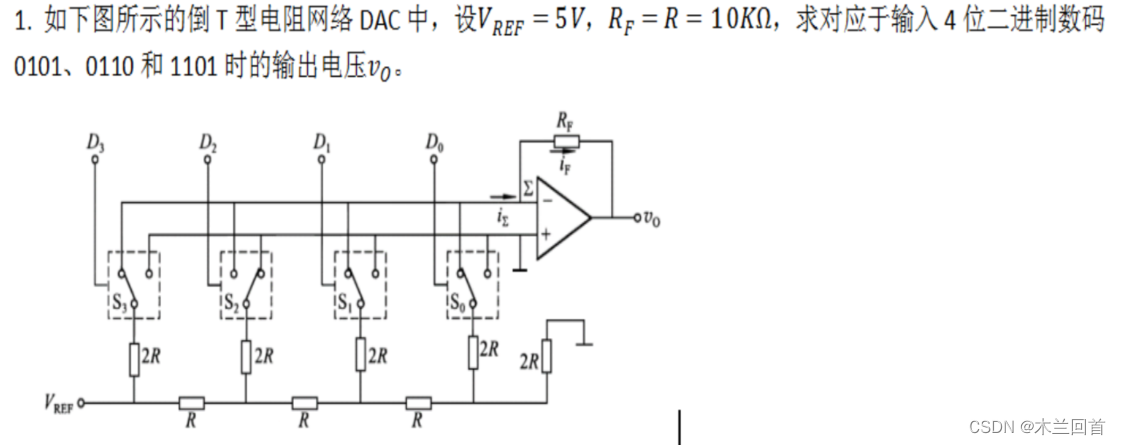

2.3R-2R倒T形电阻网络DAC

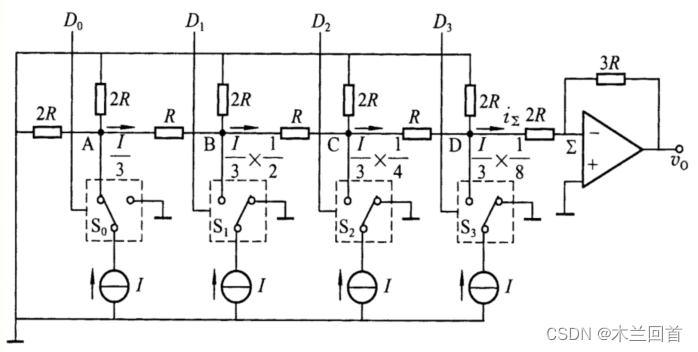

2.4单值电流型网络DAC

![]()

2.5DAC的主要指标

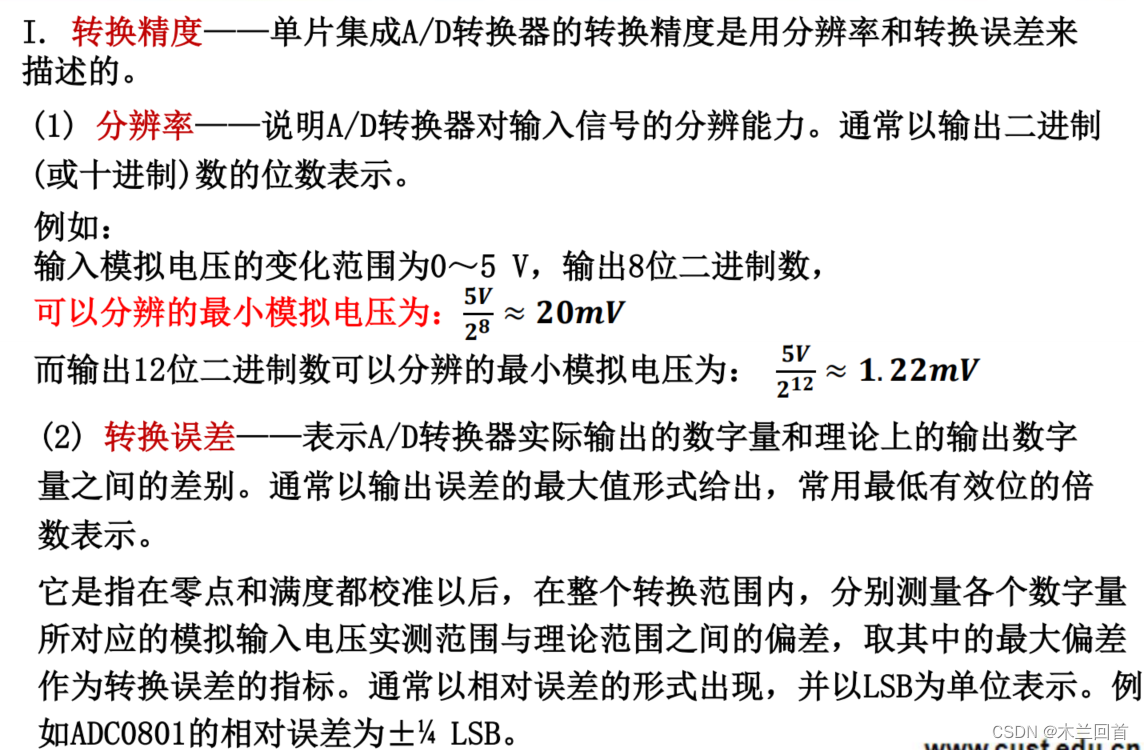

I. 转换精度

:通常用分辨率和转换误差来描述。

分辨率

:

其定义为D/A转换器模拟输出电压可能被分离的等级数。

实际应用中往往用输入数字量的位数表示D/A转换器的分辨率。

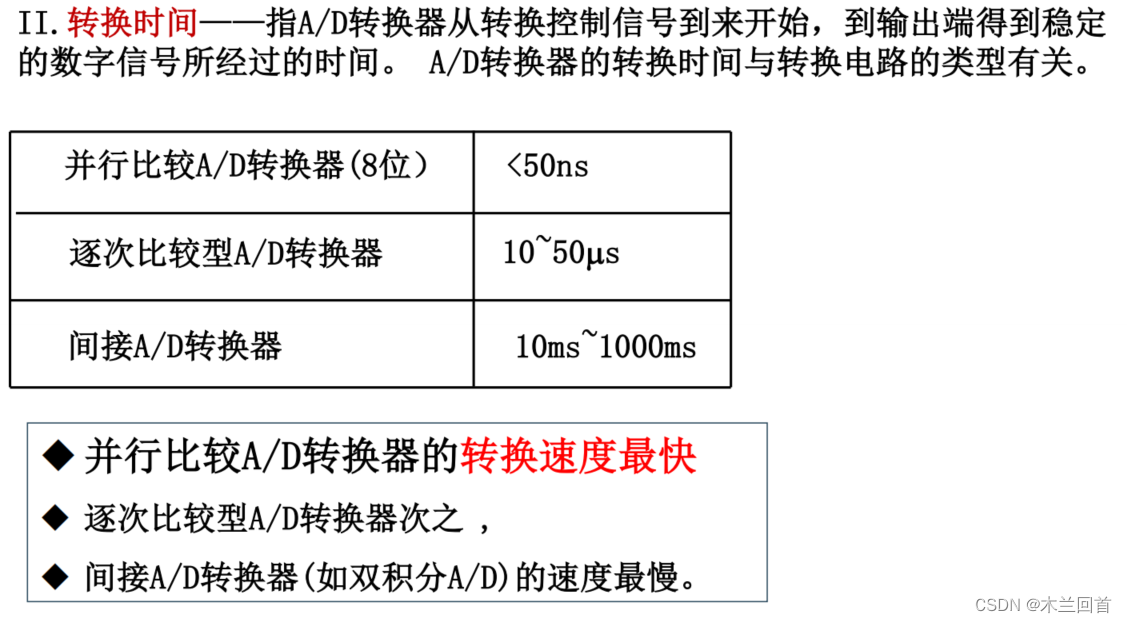

II. 转换速度

转换速度一般由建立时间决定。

建立时间:从输入由全 0 突变为全 1 时开始,到输出电压稳定

在

𝑭𝑺𝑹 ± 𝑳𝑺𝑩范围(或以𝑭𝑺𝑹 ± 𝒙%𝑳𝑺𝑩

指明范围)内为止。

建立时间是DAC的最大响应时间,所以用它衡量转换速度的快慢。

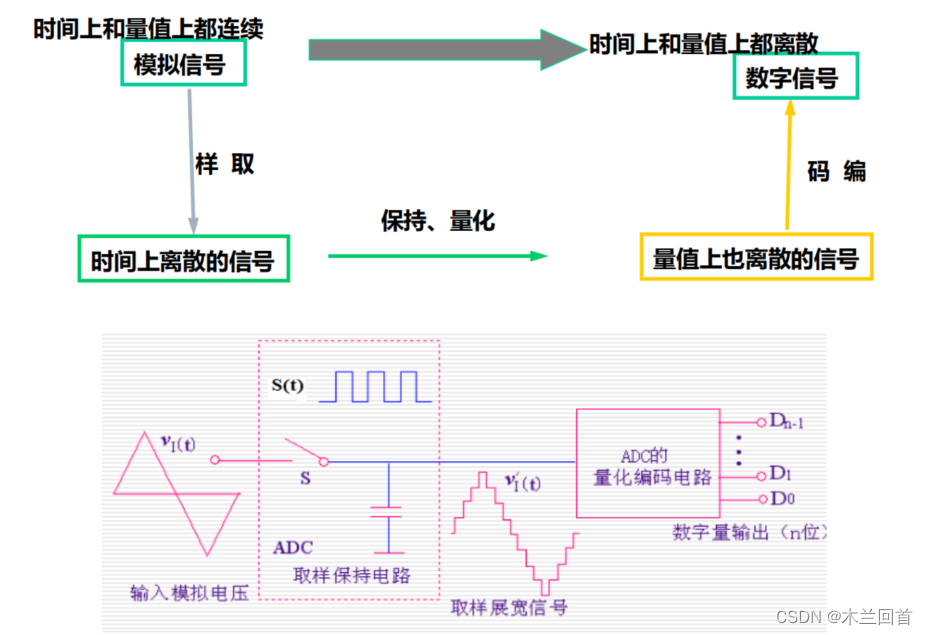

3.模数转换器(ADC)

3.1ADC的一般转换步骤

A/D

转换器一般要包括

取样, 保持,量化及编码

4

个过程。

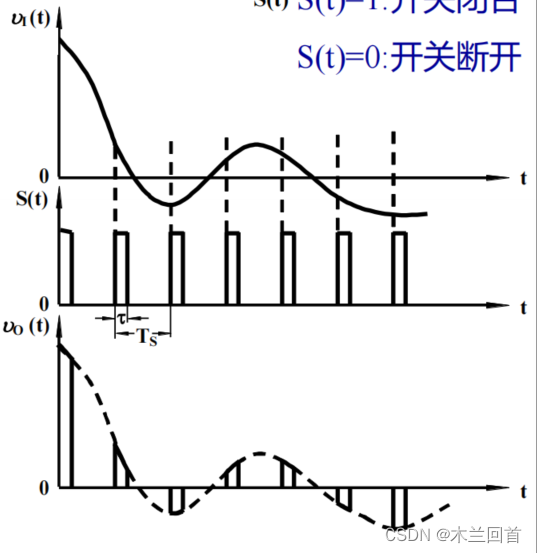

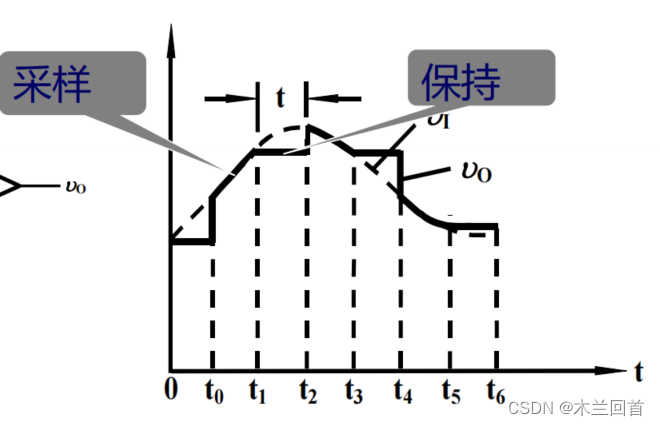

3.1.1取样与保持

采样是将随时间连续变化的模 拟量

转换

为在时间离散的模拟量

。

采样信号

S(t)

的频率愈高,所采 得信号经低通滤波器后愈能真实 地复现输入信号。合理的采样频率由采样定理确定

。

采样定理:设采样信号

S

(

t

)

的频 率为f

s

,输入模拟信号

I

(

t

)

的最 高频率分量的频率为f

imax

, 则 f

s

≥ 2

f

imax

采得模拟信号转换为数字信号都

需要一定时间

,为了给后续的

量 化编码

过程提供一个稳定的值,在取样电路后要求将所采样的模 拟信号

保持一段时间

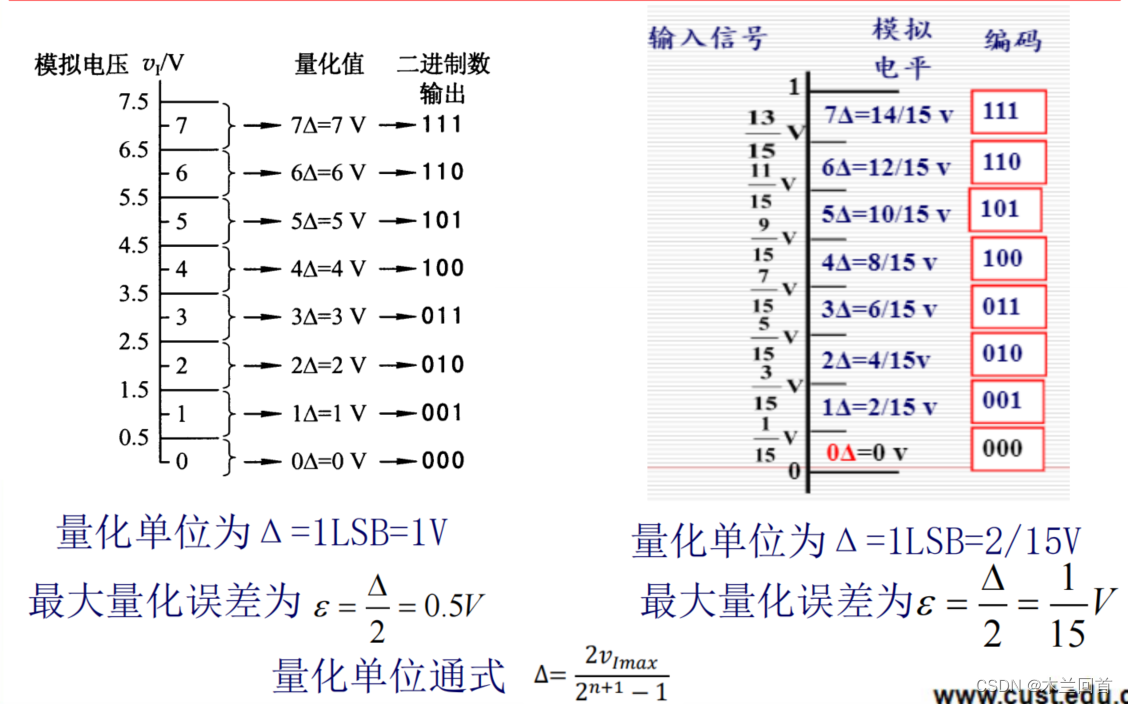

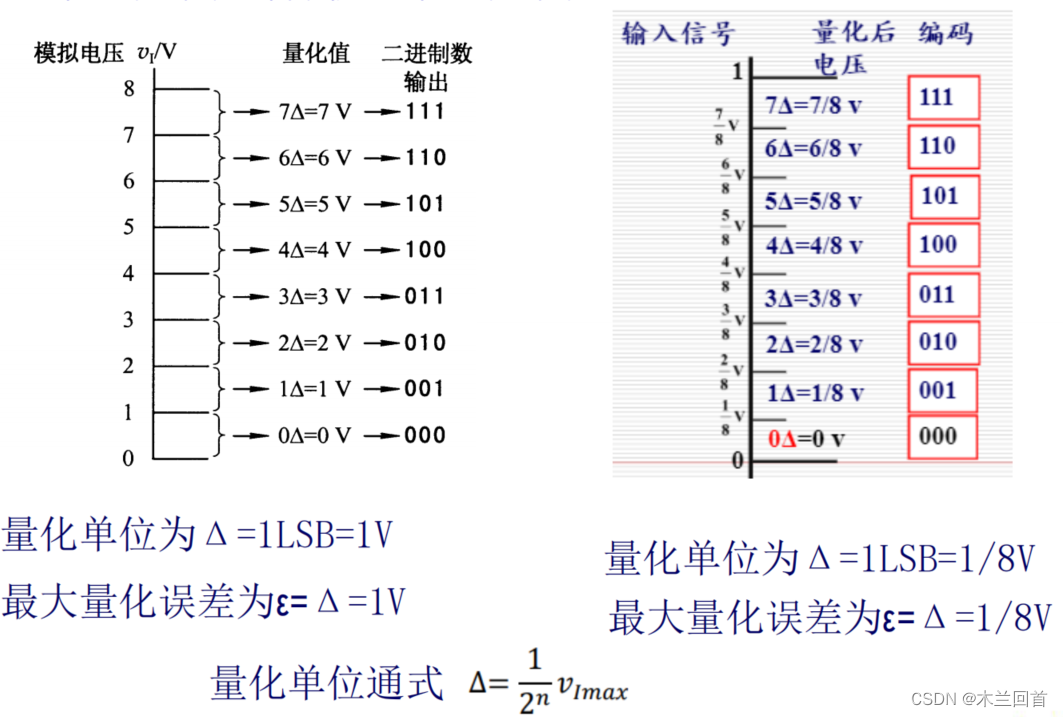

3.1.2量化和量化

量化:

任何一个数字量的大小只能是某个数量单位(LSB

)的整数倍, 因此用数字量表示取样电压值时,先要把

取样电压

化为

这个最 小单位的整数倍

,这一转换过程为量化,所取最小单位为

量化

单位

,用

Δ表示,Δ=1LSB。

编码:

量化后的数值最后还需通过编码过程用一个

代码表示出来

。

经编码后得到的代码就是

ADC

转换器输出的

数字量

。

量化误差:量化前的电压与量化后的电压差

在量化过程中由于采样电压不一定能被

整除,所以量化前后 一定存在误差,此误差称之为

量化误差

。

量化误差属原理误差,它是无法消除的。

A/D

转换器的位数越 多,各离散电平之间的差值越小,量化误差越小。

两种近似量化方式:

四舍五入法和舍去小数法

。

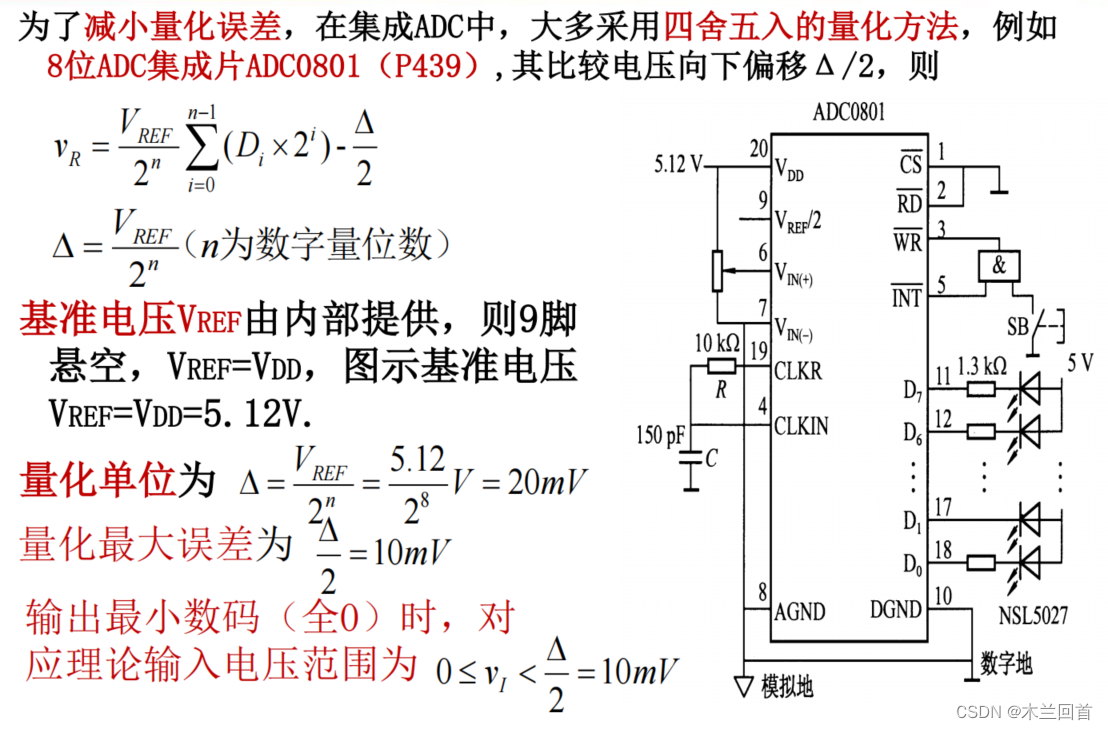

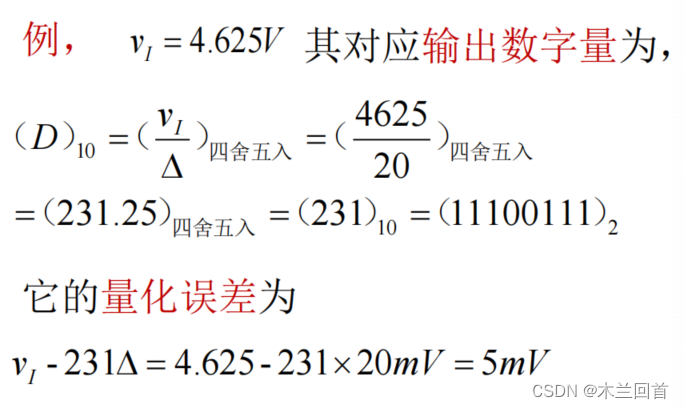

四舍五入法量化:

量化过程将不足半个量化单位部分舍弃,对于等于或大于半个量化单位部分按一个量化单位处理

舍去小数法量化:

量化中把不足一个量化单位的部分舍弃;对于等于或大于一个量化单位部分按一个量化单位处理。

ADC

种类很多,按工作原理分为直接

ADC

(并联比较型

ADC

、

逐次逼近型

ADC

。)和间接

ADC

(双积分型

ADC

)

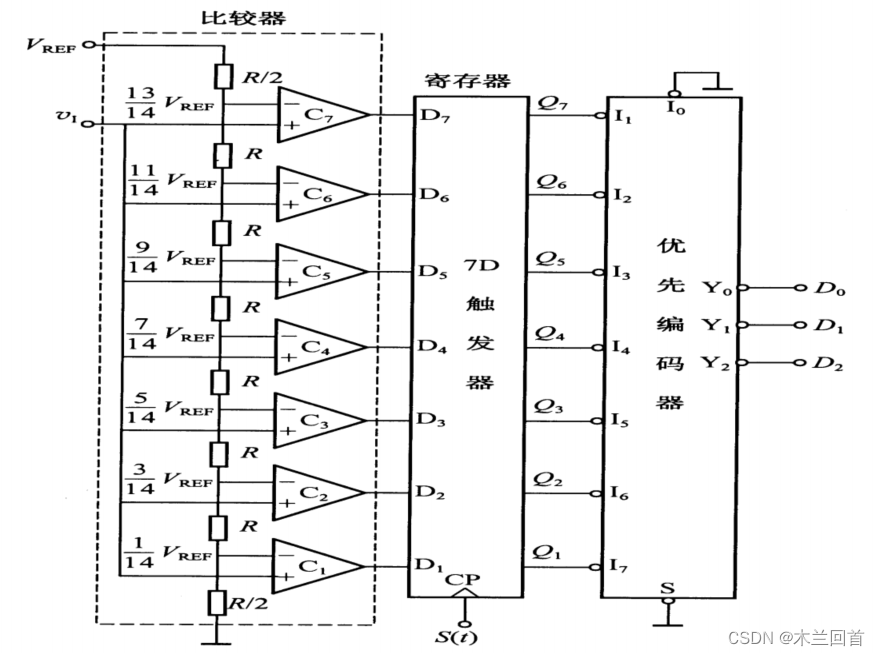

3.3

并联比较型

A/D

转换器

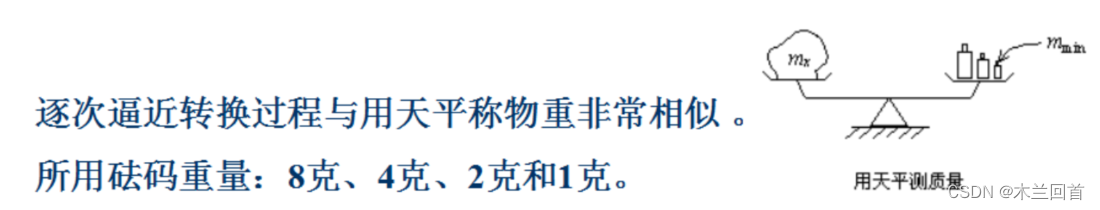

3.4逐次比较型A/D转换器

3.6集成片ADC0801

输出最大数码(全1)时,对 应理论输入电压范围为5.09V~5.11V

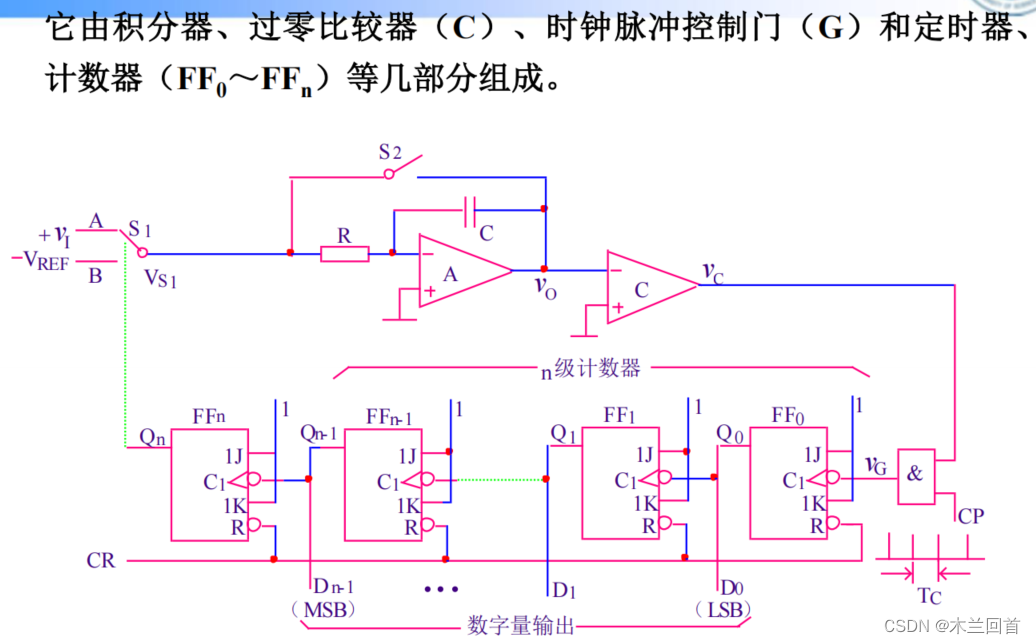

3.6双积分型ADC

双积分型ADC转换速度慢

3.7ADC的主要技术指标