SIwave仿真手册——电源完整性仿真之PDN阻抗的提取(四)

(想不到我这个弱鸡的博主有一天也有被催更的时候,看到后台被催的消息,我慌了,赶紧写一篇把。)

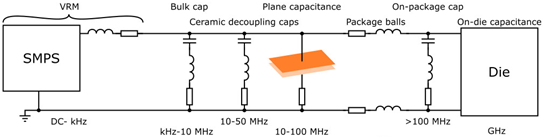

一个完整的电源分配网络(PDN)包括:电源供电端(VRM)、去耦电容、电源平面电容、用电芯片(Sink)

对于噪声的滤除,有一些经验数据供大家参考:

- VRM的去耦频率一般在100kHz以内;

- 大容量的去耦电容在1M以内;

- 高频瓷片电容的去耦电容在100MHz左右;

- 电源平面构成的平板电容的去耦频率在500MHz左右,当然这个和平面结构及材料有关系;

- 芯片封装形成的电容可达几百GHz;

- 芯片的die电容可达几GHz

电源完整性按照频率可分为:直流分析、交流分析。

直流分析:直流压降、电流密度、过孔电流

交流分析:PDN阻抗提取。

3.1 PDN阻抗的提取

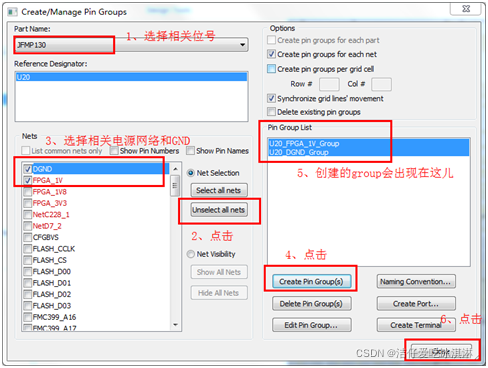

对于电源网络而言,供电引脚会有很多,如果在每个pin处都添加port,计算量太大,而且也没有必要;所以,将相同网络的pin角合并成pin group。

3.1.1手动完成PDN阻抗的提取

1、创建pin group

点击图标 →弹出下列对话框:

→弹出下列对话框:

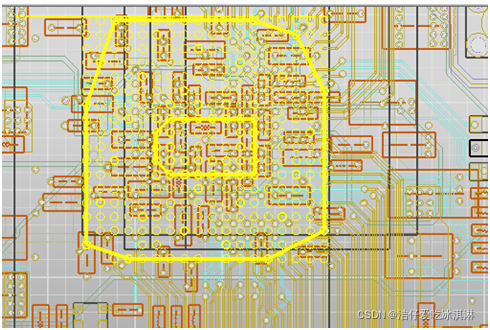

PCB界面会出现如下变化:

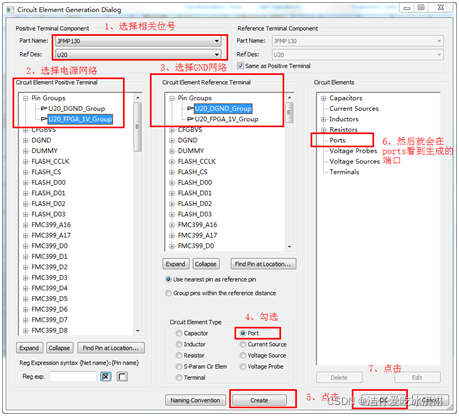

2、创建端口

点击图标  →弹出如下对话框

→弹出如下对话框

3、数据文件的清理和检查(参考1.3.4&1.3.5)

4、添加电容模型(参考2.2.1)(这一步很重要)

5、开始仿真

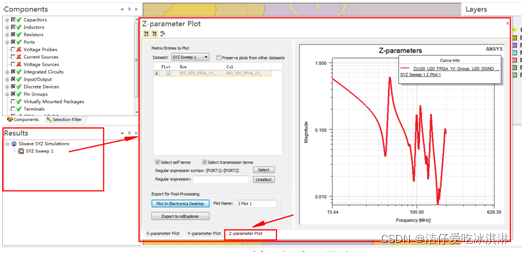

6、查看仿真结果

未添加电容模型的仿真结果如下:

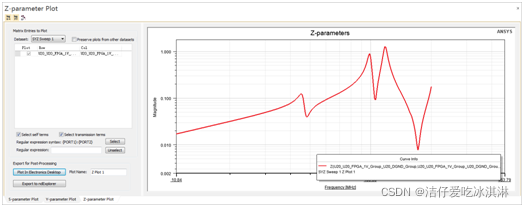

添加电容模型后的仿真结果如下:

其实可以看到两者差别还是很大的。所以要设置PDN网络上所有电容的正确型号。

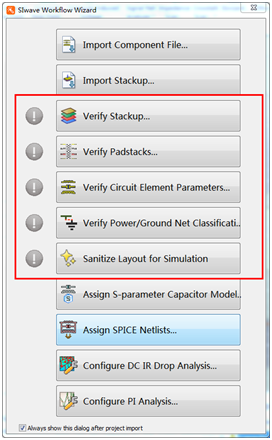

3.1.2利用向导工具完成PDN阻抗的提取

1、点击图标 →弹出如下对话框

→弹出如下对话框

2、依次确定好层叠、padstack 、电路参数、(红框中带感叹号都要确定)

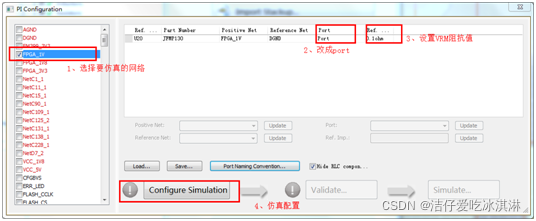

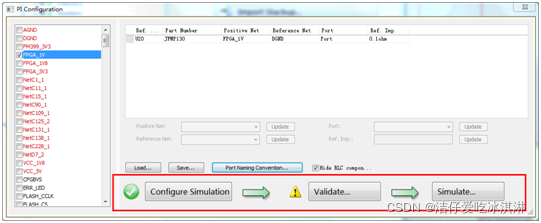

3、点击Configure PI Analysis→ 弹出如下对话框

在Ref.Imp 中填写VRM阻抗值(VRM:据说参考选用电源芯片的datasheet,但我没有找到这一项参数,听说也可以询问厂家)

VRM: Voltage Regulator Module,指板上LDO和DC-DC等电路。在几十kHz的低频范围内,VRM主要是电阻,具有较低的阻抗