vim/gvim插件-verilog autodef-自动生成

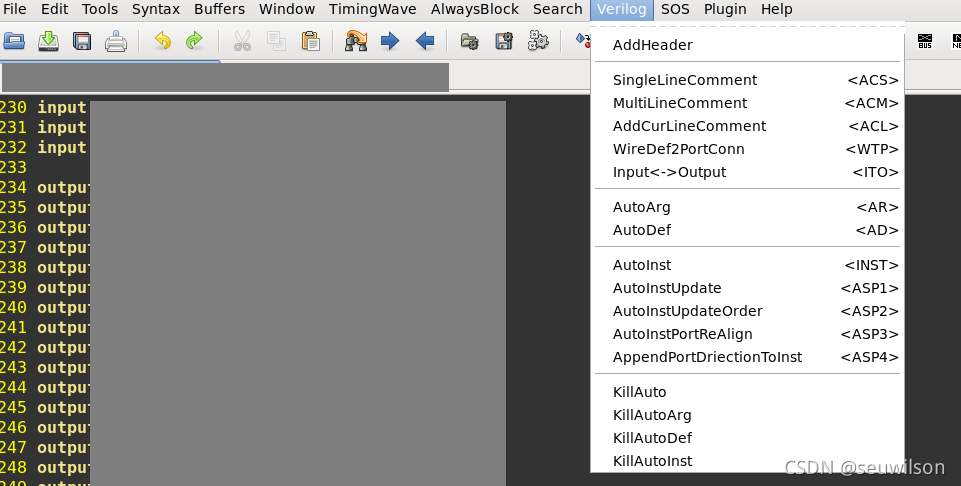

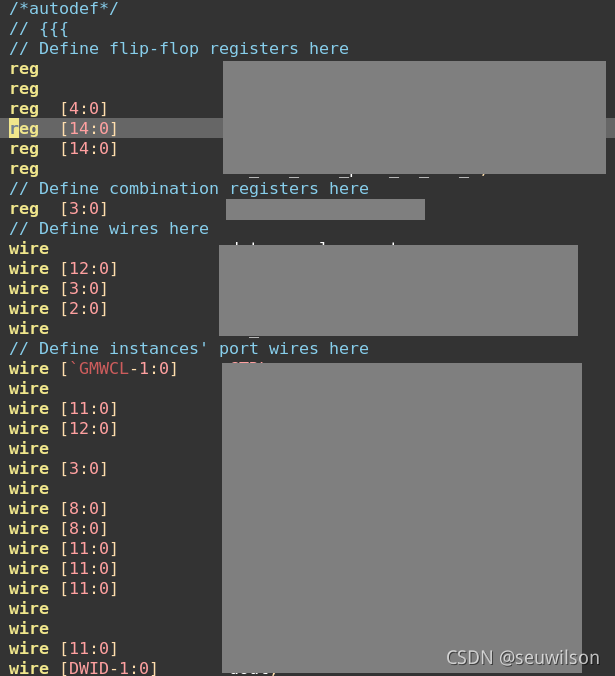

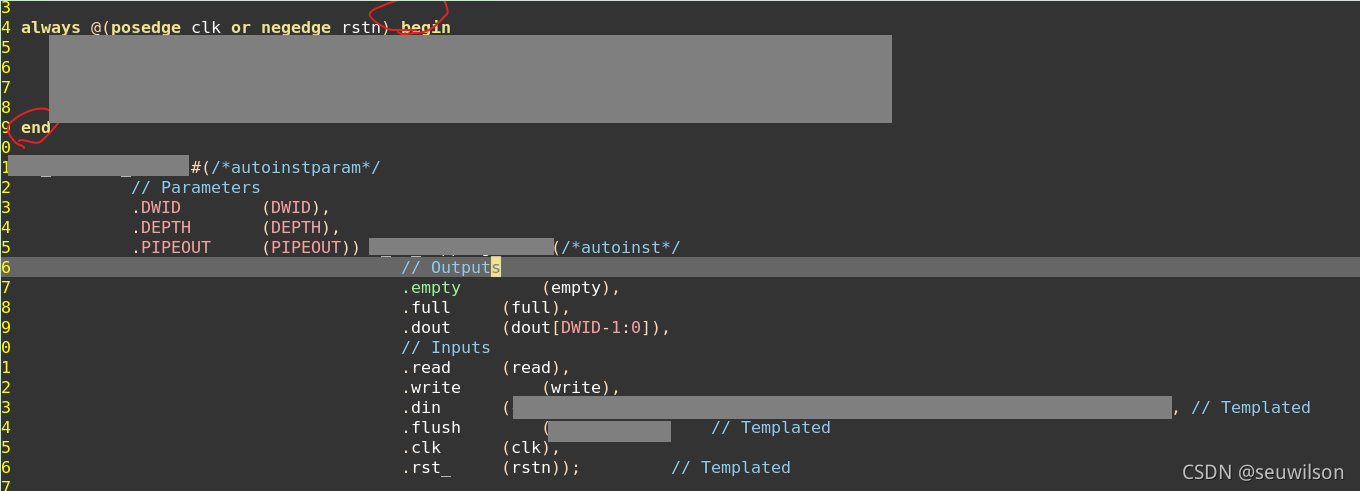

使用gvim插件效果如下

使用效果如下:

总结:

优点:

1.这个使用效果是比emacs的auto_reg和auto_wire是方便且全面的。auto_wire只能定义output的类型生成。

2.这个插件还有AutoInstPortReAlign和AppendPortDirectionToInst等功能不错。通过对齐inst input 和output代码看起来美观。

缺点:

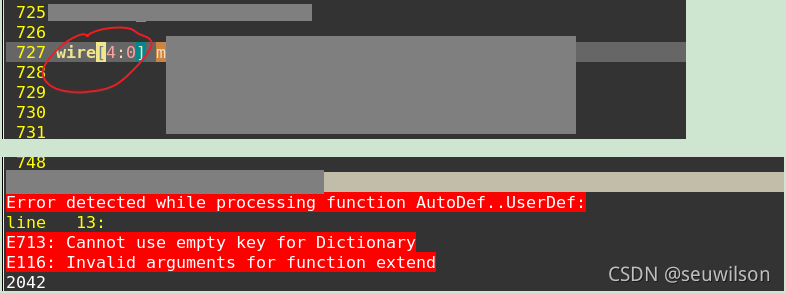

1.需要有一定的格式限制,比如不能写成wire[width-1:0],要写成assign

2.module的input 和output 没有对齐功能(目前我没发现)

为此自己单独用perl写了一个脚本来对齐

参考另一篇博客:xxxx。

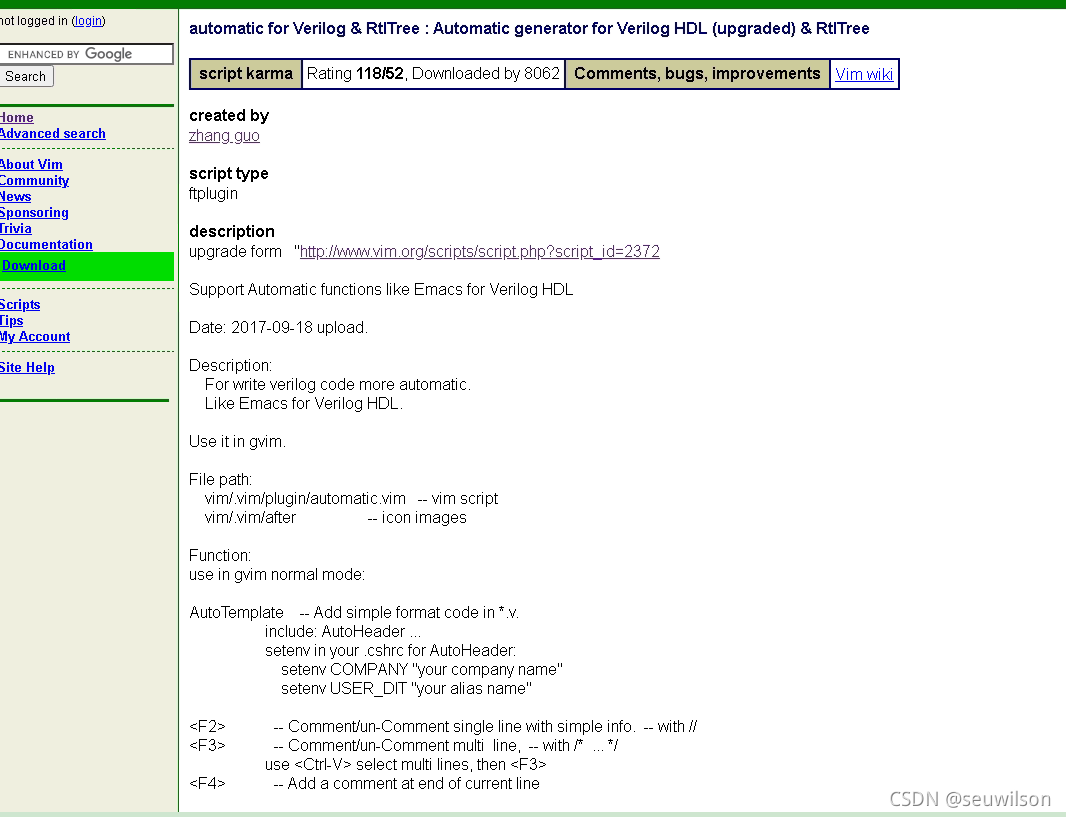

插件参考网址

https://www.vim.org/scripts/script.php?script_id=4067

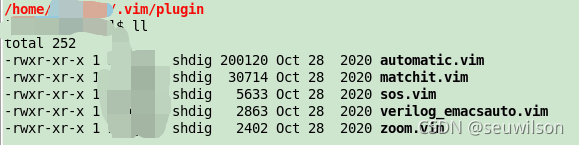

需要把automatic.vim放在指定的.vim文件夹下

使用需要注意的地方:

1.:AD 即为autodef快捷键

2.如果autoinst的port需要自动化定义,需要前面的always block 块的begin end写完整。否则无法识别(应该是脚本以begin end为识别点)

3.不能使用wire[5:0] data= xxx;写法,autodef会报错。它要识别的是assign语法