【2021山东大学数字逻辑实验2】全加器设计

实验内容:

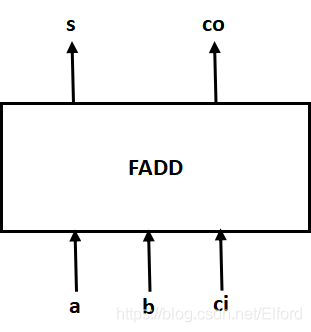

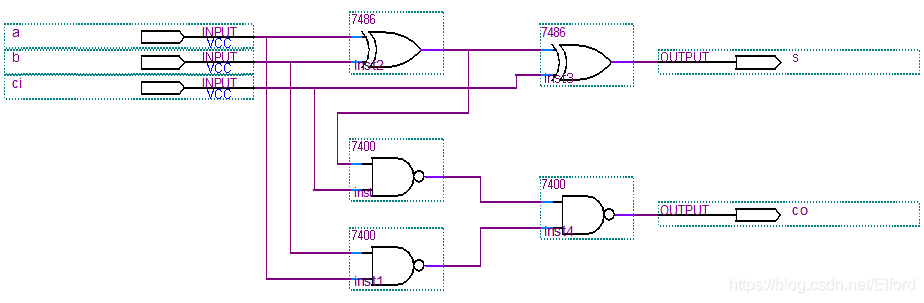

本实验要求利用两输入与非门和异或门设计一个1位二进制全加器,其中a为被加数、b为加数,ci为低位来的进位,s为本位和,co为向高位的进位,图3.4为1位二进制全加器的框图,原理图如图3.5所示。同时,要求使用并行进位实现四位加法器,并使用两组这样的加法器串行构成一个八位加法器。

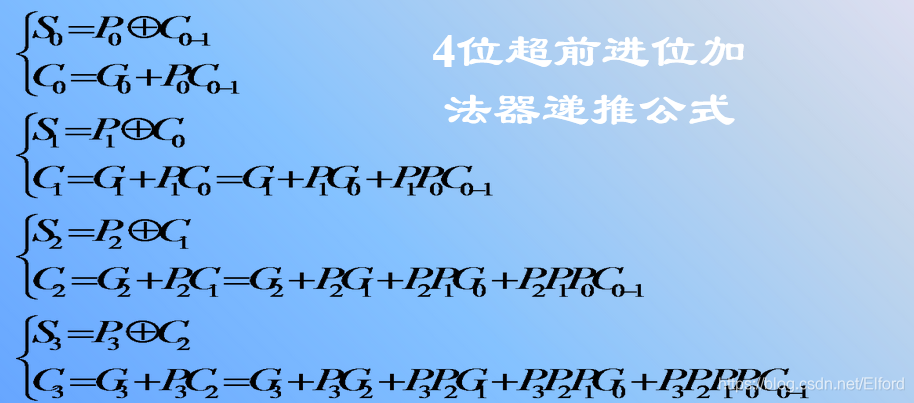

并行加法器的原理:

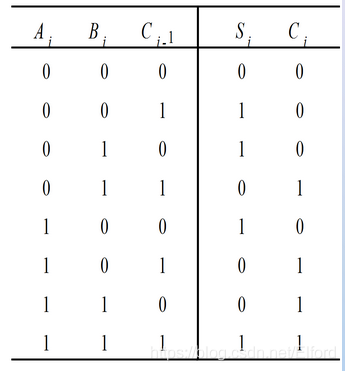

全加器真值表:

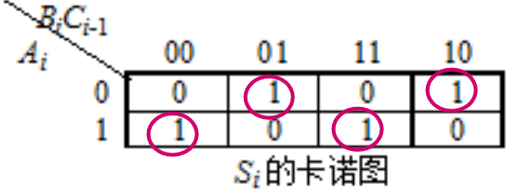

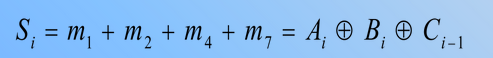

Si的卡诺图:

经过化简:

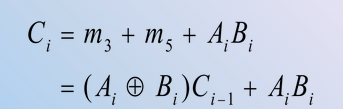

经过化简:

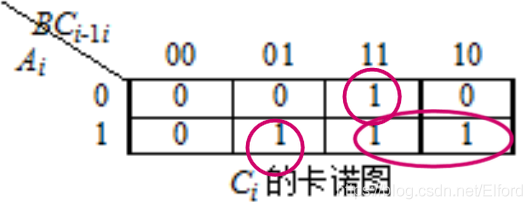

Ci的卡诺图:

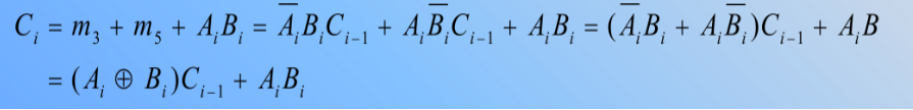

经过化简:

于是:

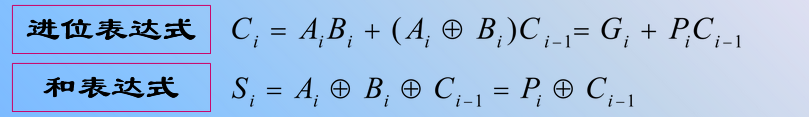

令进位生成项,进位传递条件,则:

实验原理图:

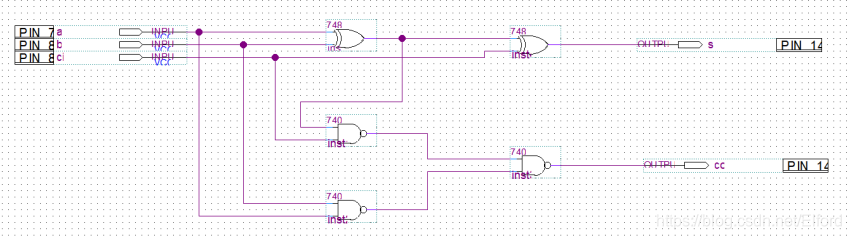

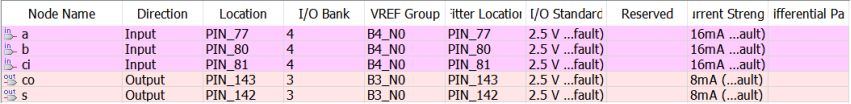

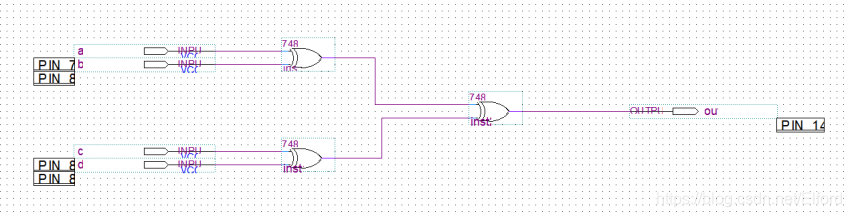

①一位全加器:

其中,输入a、b绑定在键K0、K1上,ci绑定在K2上,输出s绑定在LR0上,c0绑定在LR1上。

其中,输入a、b绑定在键K0、K1上,ci绑定在K2上,输出s绑定在LR0上,c0绑定在LR1上。

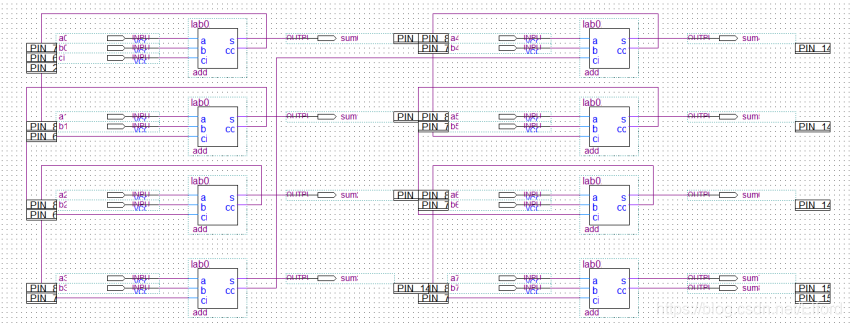

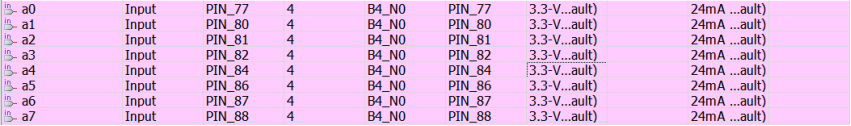

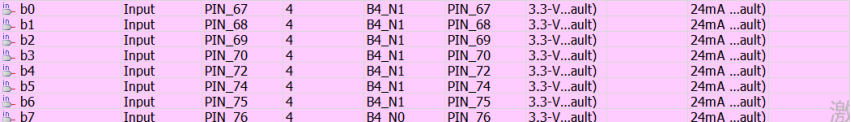

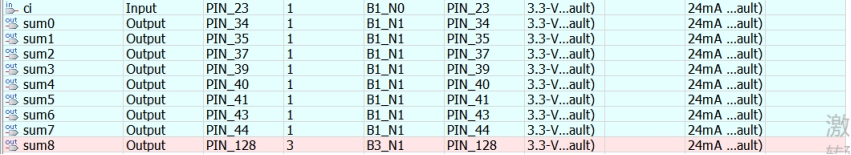

②八位加法器

其中,输入a0 ~ a7绑定在键K0 ~ K7上,b0 ~ b7绑定在键K8 ~ K15上,进位输入绑定在键K16上;输出sum0 ~ sum8绑定在键LD0 ~ LD8上。

其中,输入a0 ~ a7绑定在键K0 ~ K7上,b0 ~ b7绑定在键K8 ~ K15上,进位输入绑定在键K16上;输出sum0 ~ sum8绑定在键LD0 ~ LD8上。

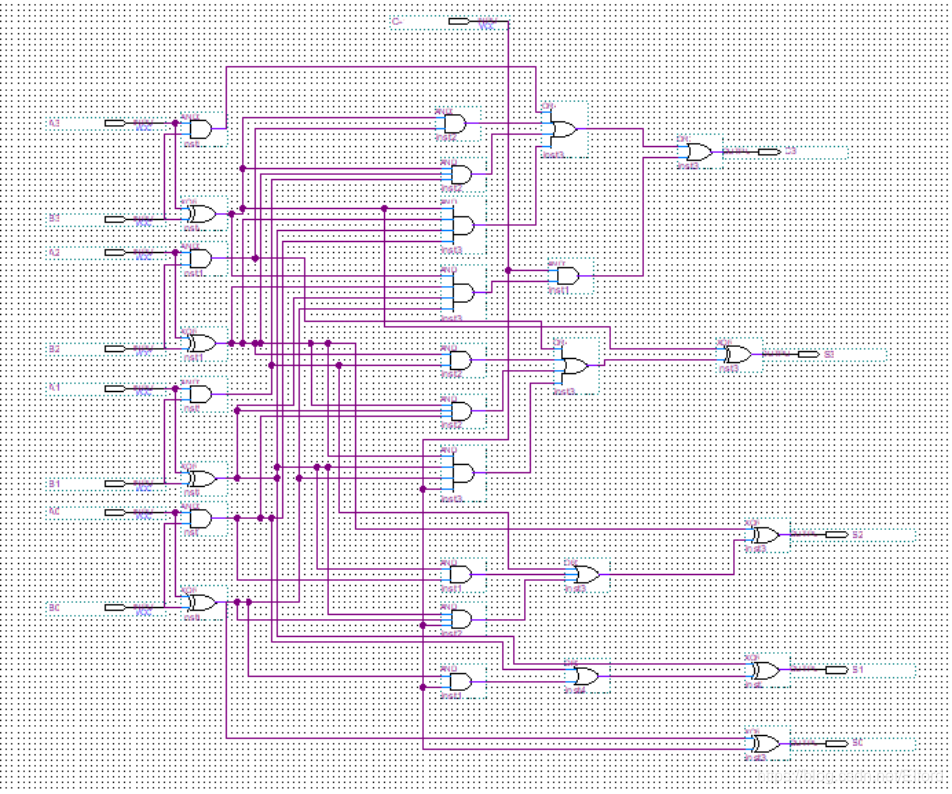

③判断BCD码的奇偶性

其中,输入a0 ~ a3绑定在键K0 ~ K3上,输出out绑定在LR0上。

其中,输入a0 ~ a3绑定在键K0 ~ K3上,输出out绑定在LR0上。

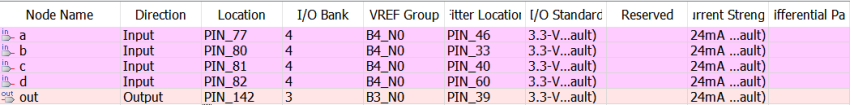

④4位并行加法器:

其中,输入B3 ~ B0、A3 ~ A0绑定在键K7 ~ K0上,输出S4 ~ S0绑定在LDR4~LDR0上。

其中,输入B3 ~ B0、A3 ~ A0绑定在键K7 ~ K0上,输出S4 ~ S0绑定在LDR4~LDR0上。

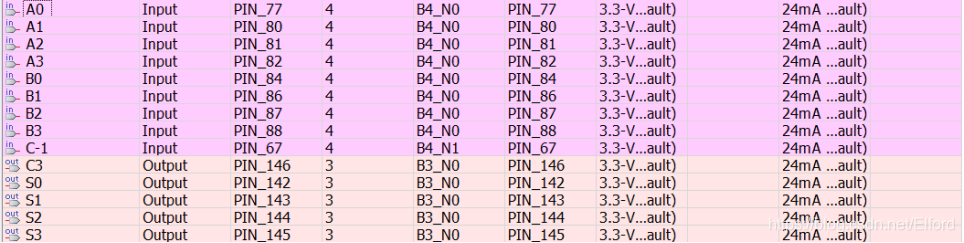

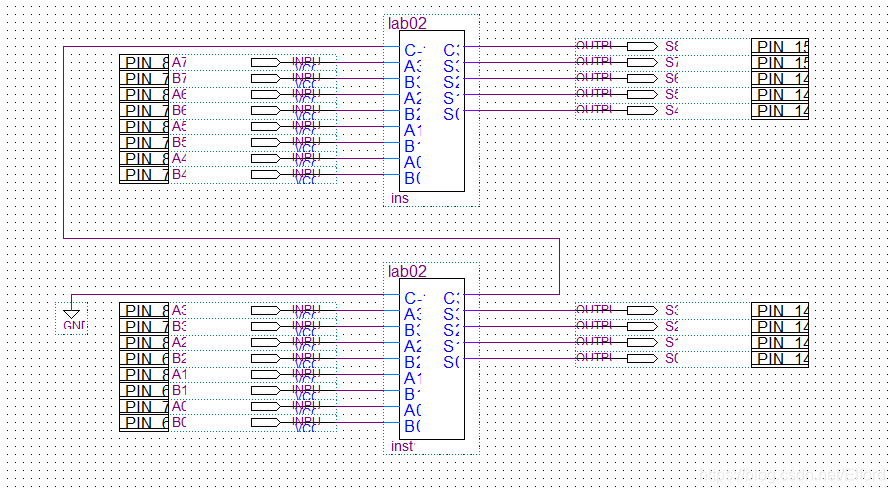

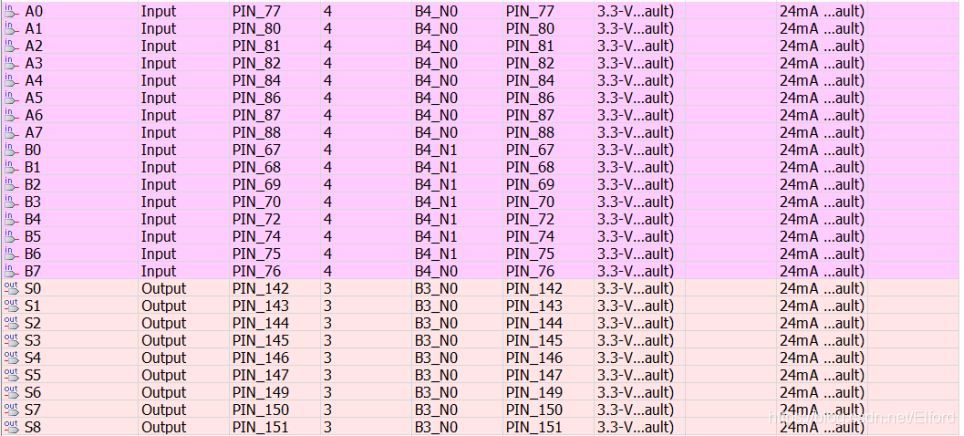

⑤两组四位并行加法器构成的八位加法器:

其中,输入B7 ~ B0绑定在键K15 ~ K8上,A7 ~ A0绑定在键K7 ~ K0上,输出S8 ~ S0绑定在小灯LDR8~LDR0上。