AXI4协议学习:架构、信号定义、工作时序和握手机制

UG1037 不是 高级微控制器总线结构(advanced micro controller bus architecture,AMBA)ARM AXI4规范的替代品,而是说明:

- 可用于创建基于AXI的IP的Xilinx工具。

- 被Xilinx采用的AXI功能。

- 将现有设计改为AXI接口的向导文件。

XIlinx 从Spartan-6和Virtex-6开始使用 高级可扩展接口(Advanced eXtensible Interface,AXI)。

1 AXI是什么?

AXI是 ARM AMBA的一部分。

AMBA 是 ARM 1996年首次引入的一种微控制器总线。2003年发行的AMBA3.0 引入了AXI。2010年发行的AMBA4.0 包含了AXI的第二版:AXI4。

Xilinx使用的就是AXI4接口。

AXI4接口的四种类型:

- AXI4(AXI4-Full): 满足高性能内存映射(memory-mapped)需求。支持256长度突发(burst)传输。

- AXI4-Lite: 对于简单的、低吞吐量的内存映射通信(例如,与控制寄存器和状态寄存器之间的通信)。不可突发传输。

- AXI4-Stream: 用于高速流数据。不需要地址,允许无限的数据突发大小。

AXI4的好处:

- 生产力:统一协议,减少学习负担。

- 灵活性:不同应用对应不同AXI4类型。

- 可用性:厂商的支持。

2 AXI怎么工作?

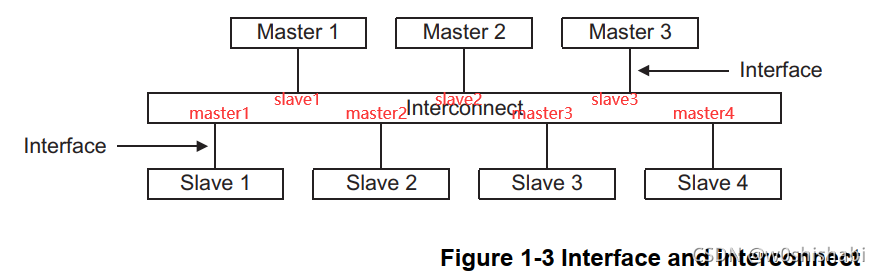

- AXI规范描述了单个AXI主(master)从(slave)之间的接口。

- 多个Master和Slave之间的内存映射可以通过Xilinx AXI Interconnect IP 和 AXI SmartConnect IP 连接在一起。

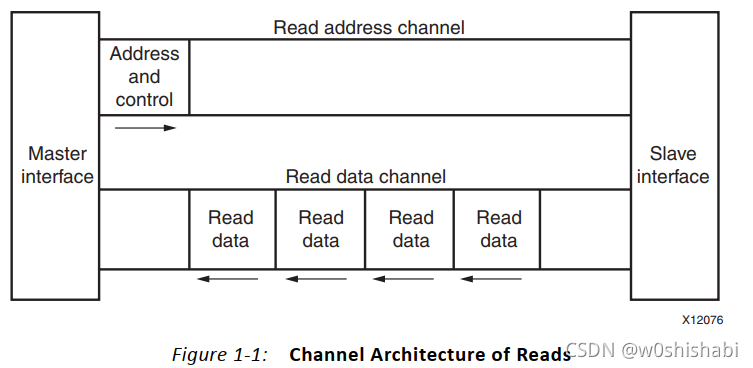

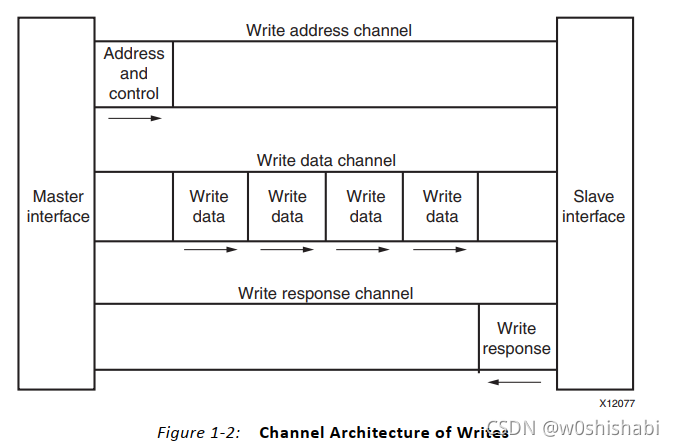

AXI4和AXI4 Lite都包含五个不同的通道:

- 读地址通道(Read Address Channel)

- 写地址通道(Write Address Channel)

- 读数据通道(Read Data Channel)

- 写数据通道(Write Data Channel)

- 写响应通道(Write Response Channel)

数据可以同时在主->从和从->主两个方向传输。数据传输的大小可以变化。

AXI4中的限制是最多256个数据传输的突发事务。AXI4-Lite只允许每个事务进行1个数据传输。

AXI4读事务 使用 读地址 和 读数据 通道示意:

AXI4写事务 使用 写地址 和 写数据 通道示意:

AXI4:

- 读或写事务的 地址 与 数据 的连接分离。所以可以同时、双向 传输。

- 一个读或写地址后可以跟着256个突发数据传输。

除了突发特性外,还有:

- data upsizing and downsizing

- multiple outstanding addresses

- out-of-order transaction processing

硬件层面,AXI4允许每个AXI master-slave的工作时钟不同。而且AXI4可以通过打拍来改善时序。

AXI4-Lite:

- 与AXI4比不支持突发。所以少很多接口

AXI4-Stream:

- 定义传输流数据的单一通道( write data channel )。

- 可以进行无限制长度的突发传输。

Infrastructure IP: 基础设施IP是一些帮助系统连接的支持IP。基础设施IP往往是一种通用IP,它使用通用的AXI4接口在系统中移动或转换数据,而不解释数据。这些IP对于将IP连接到一个系统很有用,但通常不是数据的endpoint。例子:

- AXI Register slices(打拍用)

- AXI FIFOs(缓冲/时钟转换)

- AXI Interconnect IP 和 AXI SmartConnect IP(连接内存映射IP)

- AXI Direct Memory Access (DMA) engines(内存映射到stream的转换)

- AXI Performance Monitors and Protocol Checkers(分析与debug)

- AXI Verification IP(用于基于仿真的验证和性能分析)

AXI4-Stream与 Memory-Mapped协议的结合:

一种常见的方法是构建将 AXI4-Stream 和 AXI内存映射 IP组合在一起的系统。通常可以使用AXI Direct Memory Access (DMA) engines将Stream移进或移出内存。

例如,处理器可以使用DMA引擎解码数据包或在流数据之上实现协议栈,以构建更复杂的系统,其中数据在不同的应用程序空间或不同的IP之间移动。

3 AXI协议

3.1 架构

3.1.1 通道定义

5个通道

3.1.2 接口与互连(interconnect)

AXI协议描述了下面的接口定义:

- master与互连之间

- slave与互连之间

- master与slave之间

接口定义支持各种不同的互连实现。互连相当于内部具有对称的主和从端口的设备,真实的主和从设备可以连接到这些端口。

3.1.3 Register slices

每个AXI通道只在一个方向上传输信息,各通道之间没有固定的关系。这个重要的特性使得可以在任何通道插入寄存器,但要付出额外的延迟周期。

也可以在给定互连的几乎任何点上使用寄存器。在处理器和高性能内存之间使用直接、快速的连接是有好处的,但是使用简单的寄存器将较长的路径隔离到性能不那么关键的外围设备。

3.2 基本事务

三个示例:

- 突发读示例

- 重叠突发读

- 突发写

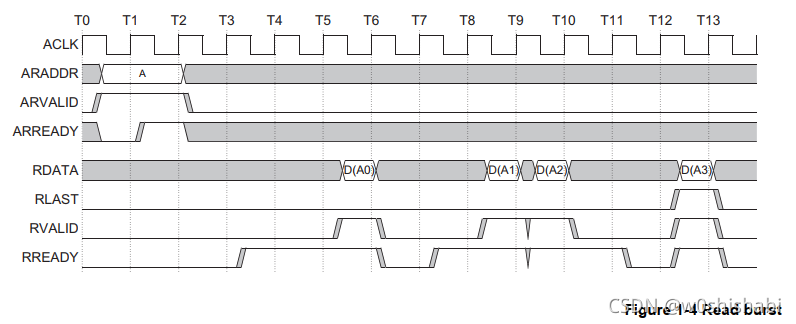

注意各示例的VALID和READY的握手机制,只有VALID和READY都为高才进行地址和数据的传输。

3.2.1 突发读示例

下图是长度为4的突发读时序(省略其他控制信号):

- 当ARVILID和ARREADY都为高,地址被传递给从接口。

- 当RVALID和RREADY都为高,数据被传递给从接口。

- RLAST与第四个有效数据同步,表示最后一个数据。

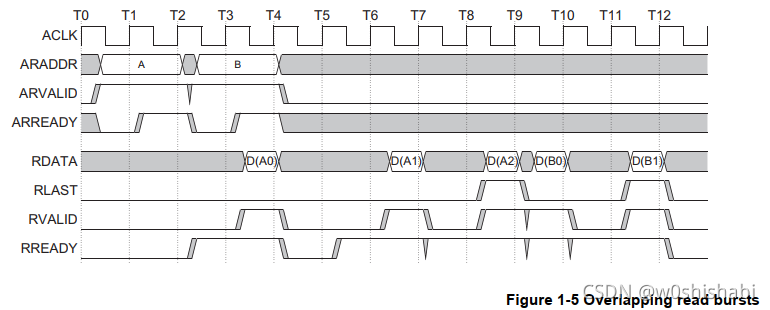

3.2.2 重叠突发读示例

当从接口接收了第一个地址后,master接口可以发送另一个突发地址。使得当第一个突发读结束后,紧跟着第二个突发读。

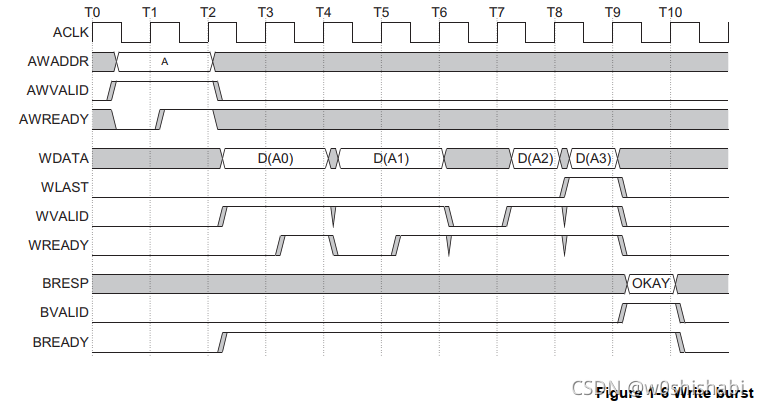

3.2.3 突发写示例

与突发读类似,都需要在握手完成时传递信息。

当从服务器接受了所有的数据项后,它会向主服务器发送一个写响应,以表明写事务已经完成。

3.2.4 事务顺序

AXI协议支持无序(Out-of-order)的事务完成。它为跨接口的每个事务提供ID标记。该协议要求具有相同ID标记的交易按顺序完成,但具有不同ID标记的交易可以不按顺序完成。

无序事务可以通过两种方式提高系统性能:

- 互连可以使 具有快速响应的slave的事务 在 更早发生的带有较慢响应的slave的事务 之前完成。

- 复杂的slave可以无序的返回读取的数据。比如,后访问的数据项可能在早期访问的数据之前进入内部缓冲区。

如果主服务器要求事务按照发出的顺序完成,那么它们必须都有相同的ID标签。但是,如果主服务器不要求按顺序完成交易,它可以为交易提供不同的ID标记,使它们能够按任何顺序完成。

在多master系统中,互连器负责向ID标签附加附加信息,以确保来自所有master的ID标签是唯一的。ID标记类似于主编号,但是有了扩展名,每个master可以通过提供一个ID标记来指示虚拟master编号,从而在同一端口内实现多个虚拟master。

虽然复杂的设备可以使用这种无序的功能,但简单的设备并不需要使用它。简单的主服务器可以使用相同的ID标签发出每个事务,而简单的从服务器可以按照顺序响应每个事务,而不考虑ID标签。

3.3 额外的功能

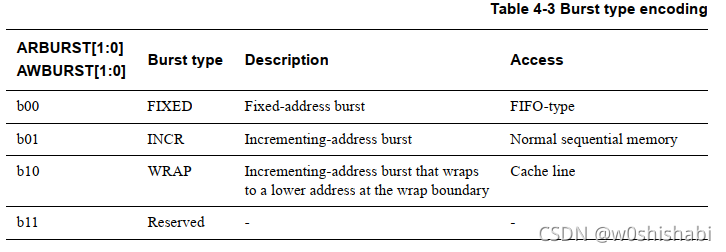

- 突发类型:

- normal memory accesses

- wrapping cache line bursts

- streaming data to peripheral FIFO locations

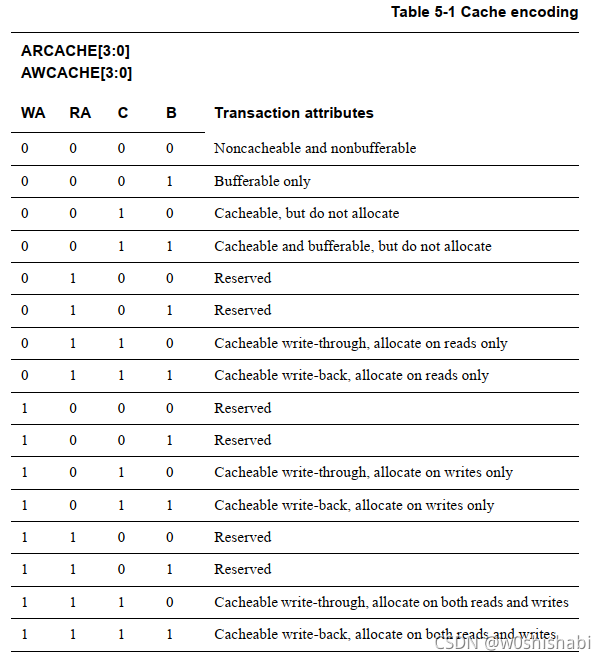

- 支持系统缓存:

AXI协议的缓存支持信号 使master能够向系统级缓存提供事务的可缓冲、可缓存和分配属性。

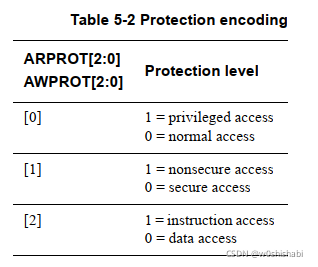

- 支持保护单元:

为了允许私有访问和安全访问,AXI协议提供了三个级别的保护单元支持。

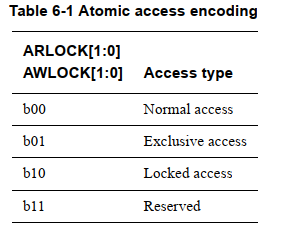

- 原子操作:

AXI协议定义了独占访问和锁定访问的机制。

- 错误支持:

AXI协议为地址解码错误和从服务器产生的错误提供错误支持。

- 不对齐的地址:

为了提高突发的初始访问性能,AXI协议支持非对齐的突发起始地址。

4 信号定义

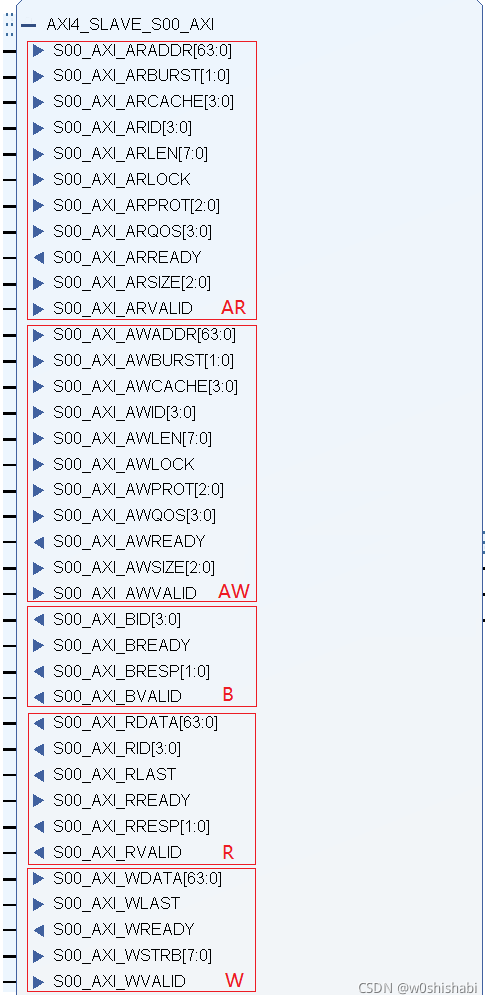

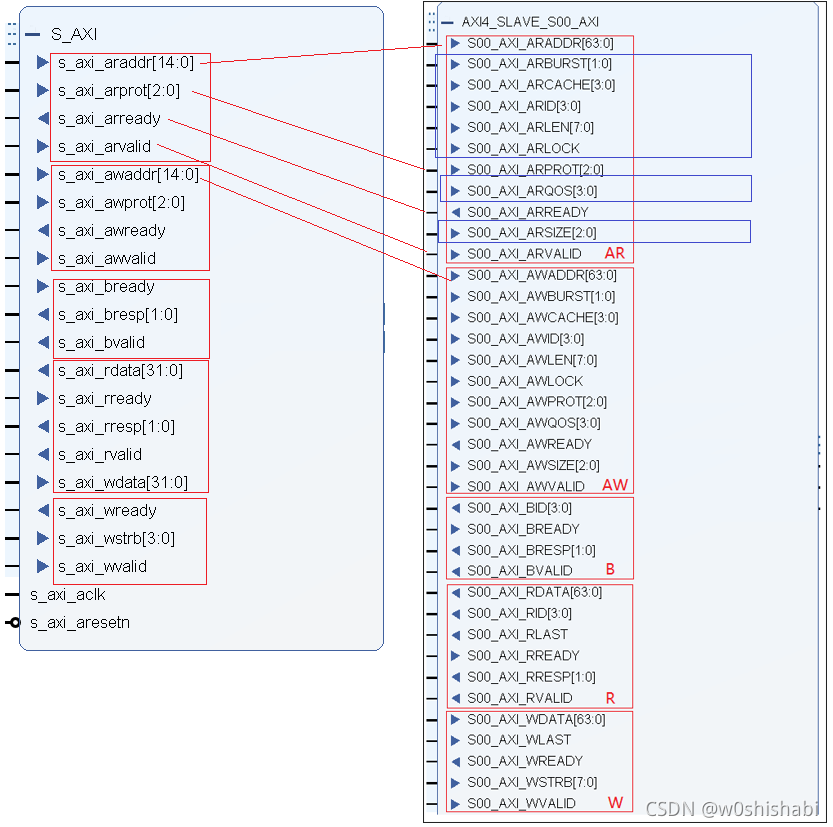

Xilinx IP 核中的AXI4-full接口,可以看到每组信号都用名字开头的字母来区分。

4.1 全局信号

| 信号 | 源 | 描述 |

|---|---|---|

| ACLK | 时钟源 | 全局时钟信号,所有信号在这个时钟的上升沿采样 |

| ARESETn | 复位源 | 全局复位信号,低电平有限 |

4.2 写地址通道信号

| 信号 | 源 | 描述 |

|---|---|---|

| AWID[x:0] | master | 写地址ID。这个信号是写地址组信号的标识标签。 |

| AWADDR[x:0] | master | 写地址。写地址总线给出写突发事务中第一次传输的地址。关联的控制信号用于确定突发中剩余传输的地址 |

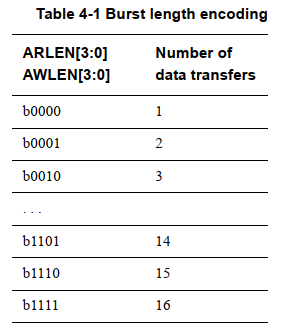

| AWLEN[3:0] | master | 突发长度。突发长度给出了突发传输的确切数字。这个信息决定了与该地址相关联的数据传输的数量。突发长度=数据总长-1 |

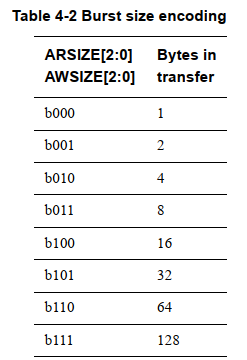

| AWSIZE[2:0] | master | 突发尺寸。这个信号表示突发事件中每个传输的大小。另外配合字节通道选通信号(strobe,WSTRB)准确地指示要更新的字节通道。 |

| AWBURST[1:0] | master | 突发类型。突发类型,加上大小信息(AWSIZE),详细说明了如何在突发中计算每个传输的地址。 |

| AWLOCK[1:0] | master | 锁类型。这个信号提供有关转移的原子特性的附加信息。 |

| AWCACHE[3:0] | master | 缓存类型。这个信号指示事务的可缓冲(bufferable)、可缓存(cacheable)、透写(write-through)、回写(write-back)和分配(allocate)属性。 |

| AWPROT[2:0] | master | 保护类型。该信号指示传输事务的正常(normal)、私有(privileged)或安全保护(secure protection)级别,以及事务是数据访问(data access )还是指令访问(instruction access)。 |

| AWVALID | master | 写地址有效。该信号表示有效的写地址和控制信息可用:1 =地址和控制信息可用0 =地址和控制信息不可用。地址和控制信息保持稳定,直到地址确认信号AWREADY变为HIGH。 |

| AWREADY | slave | 写地址准备好。这个信号表明从机准备好接受一个地址和相关的控制信号:1 =从机准备好了0 =从机还没有准备好。 |

4.3 写数据通道信号

| 信号 | 源 | 描述 |

|---|---|---|

| WID[x:0] | master | 写ID标签。这个信号是写数据传输的ID标签。WID值必须与写事务的AWID值匹配。 |

| WDATA[x:0] | master | 写数据。写数据总线可以是8、16、32、64、128、256、512或1024位宽。 |

| WSTRB[3:0] | master | 写选通(strobe)。这个信号指示内存中要更新的字节位置。写数据总线的每8位都有一个写选通。因此,WSTRB[n]对应于WDATA[(8 × n) + 7:(8 × n)],即每一位选通自己对应的Byte |

| WLAST | master | 写last。这个信号表示写入突发中的最后一次传输。 |

| WVALID | master | 写有效。这个信号表示有效的写数据和选通可用:1 = 写数据和WSTRB可用 ; 0 =写数据和WSTRB不可用。 |

| WREADY | slave | 写ready。这个信号表示从机可以接受写数据:1 = slave就绪 0 = slave未准备好 |

4.4 写响应通道信号

| 信号 | 源 | 描述 |

|---|---|---|

| BID[x:0] | Slave | 响应ID。写响应的标识标签。BID值必须匹配slave正在响应的写事务的AWID值。 |

| BRESP[1:0] | Slave | 写响应。这个信号指示写事务的状态。允许的响应有OKAY、EXOKAY、SLVERR和DECERR。 |

| BVALID | Slave | 写响应有效。这个信号表明一个有效的写响应是可用的:1 =写响应可用0 =写响应不可用。 |

| BREADY | master | 响应ready。这个信号表示主机可以接受响应信息。1 = master就绪0 = master未就绪 |

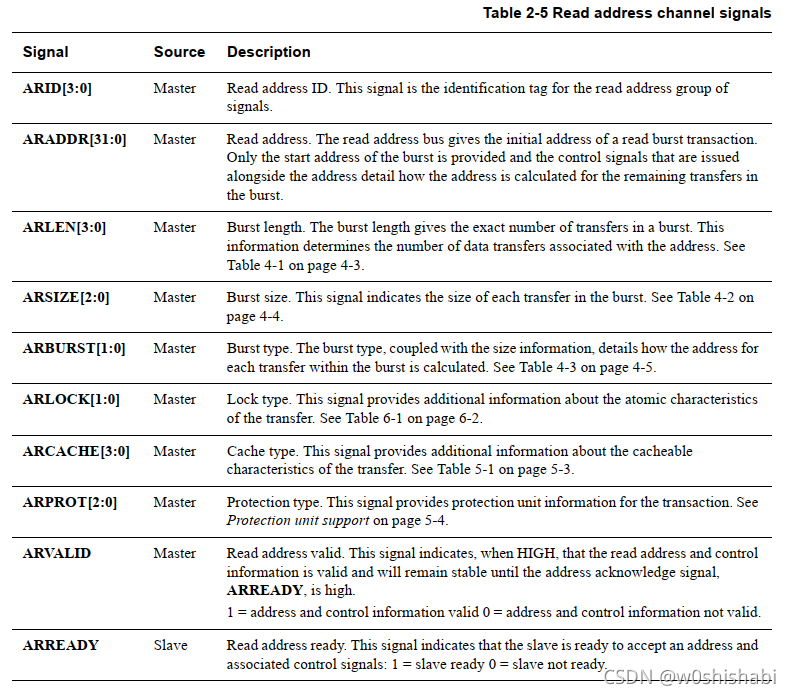

4.5 读地址通道信号

与写地址通道类似:

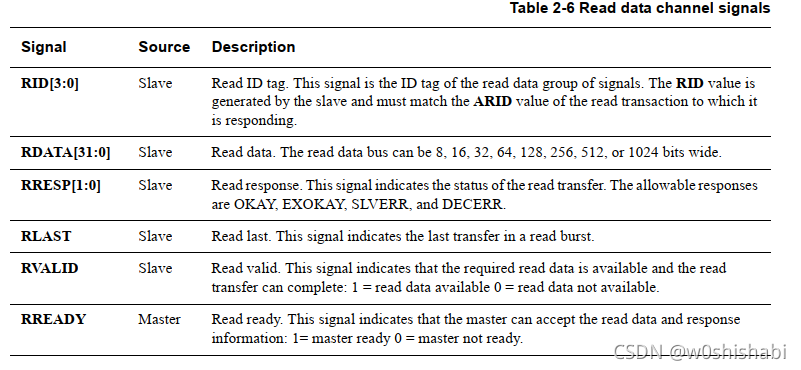

4.6 读数据通道信号

与写数据通道类似:

4.7 低功耗接口信号

| 信号 | 源 | 描述 |

|---|---|---|

| CSYSREQ | 时钟控制器 | 系统低功耗的要求。这个信号是系统时钟控制器要求外设进入低功耗状态的请求。 |

| CSYSACK | 外围设备 | 低功耗要求确认。这个信号是对系统低功耗请求的外设的确认。 |

| CACTIVE | 外围设备 | 时钟有效。这个信号表明外设需要它的时钟信号:1 =需要外设时钟0 =不需要外设时钟。 |

4.8 字段定义的简单说明:

AWLEN[3:0]、ARLEN[3:0]:

AWSIZE[2:0]、ARSIZE[2:0]:

AWBURST[1:0]、ARBURST[1:0]:

AWLOCK[1:0]、ARLOCK[1:0]:

AWCACHE[3:0]、ARCACHE[3:0]:

AWPROT[2:0]、ARPROT[2:0]:

4.9 AXI-Lite与AXI-stream的接口

AXI-Lite:

可以看到,AXI-Lite因为不支持突发传输,所以端口上没有与突发相关的信号。其他控制信号也减少了一部分,就是AXI4-full的简化版。

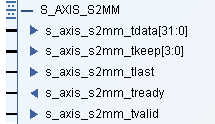

AXI-stream:

AXI-stream则可以看作只有一个写数据端口,其突发长度是不受限的。

5 通道握手机制

5.1 握手过程

所有的5个通道都需要进行VALID/READY握手才能传输数据和控制信号。这种双向流量控制机制使主从双方都能控制数据和控制信息移动的速率。源产生VALID信号以指示何时数据或控制信息可用。目的地生成READY信号来表示它接受数据或控制信息。只有当VALID和READY信号都是HIGH时,才会发生传输。

在主接口和从接口上的输入和输出信号之间必须没有组合逻辑路径。

5.2 通道之间的关系

地址、读、写和写响应通道之间的关系是灵活的。

例如,写数据可以在对应写地址之前出现。当写地址通道包含比写数据通道更多的寄存器阶段时,就会发生这种情况。写数据也可能出现在与地址相同的周期中。

但是当互连线必须确定目的地址空间或slave地址空间时,必须重新排列地址并写入数据。这是必需的,以确保写入数据仅对它的目的slave有效。

此时必须维持的两种关系是:

- 读取数据必须始终在与数据相关的地址之后。

- 写响应必须始终在与写响应相关的写事务中的最后一个写传输之后。

5.3 通道握手信号之间的依赖关系

为了防止死锁,必须观察握手信号之间存在的依赖关系。

在任何事务中:

- 事务中一个AXI组件的VALID信号不能依赖于另一个组件的READY信号。

- READY信号可以等待VALID信号的断言。

注意:虽然在断言READY之前等待VALID被断言是可以接受的,但默认情况下在断言VALID之前断言READY也是可以接受的,这可以导致更有效的设计。

- 实际上,在比如Xilinx BRAM等IP中,都是先给VALID,对应的READY才会拉高,所以等READY在使能VALID是不对的工作时序。

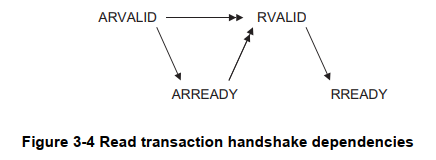

读事务握手信号的关系:

- 单箭头指向 可以在前一个信号(本信号)断言之前或之后断言的信号(指向的信号)。

- 双箭头指向 只有在前一个信号(本信号)断言之后才可以断言的信号(指向的信号)。

所以slave 在断言读取的数据有效信号RVALID之前,必须等到ARVALID与ARREADY断言后。

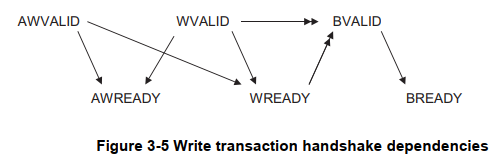

写事务握手信号的关系:

- 单箭头指向 可以在前一个信号(本信号)断言之前或之后断言的信号(指向的信号)。

- 双箭头指向 只有在前一个信号(本信号)断言之后才可以断言的信号(指向的信号)。

6 AXI4相关文件

- LogiCORE IP AXI Interconnect IP Product Guide (PG059)

- LogicCORE IP AXI SmartConnect Product Guide (PG247)

- LogicCore IP AXI4-Stream Interconnect Product Guide (PG085)